Telink B91 Driver SDK

Overview

The Telink B91 Driver SDK Developer Handbook applies to the Telink TLSR921x and TLSR951x series chips.

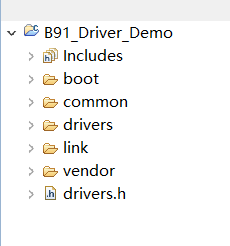

Driver directory structure

The Driver SDK directory structure is as follows:

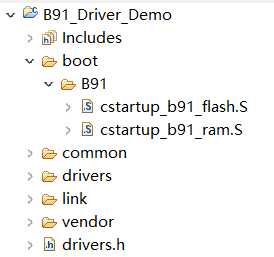

boot

Under this folder are the boot files.

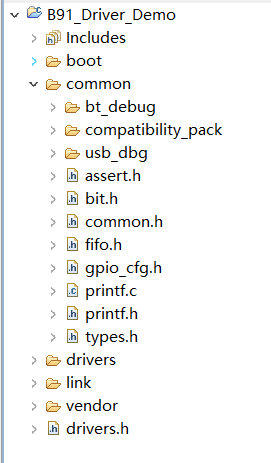

common

Under this folder are some common files that are not related to the driver. Two of the folders are described in particular:

bt_debug: is the interface function for Bluetooth related modules to set debug GPIO.

compatibility_pack: is to be compatible with the previous driver interface of each SDK, the relevant files added will not be used in the driver.

drivers

This folder is for the driver of relevant module.

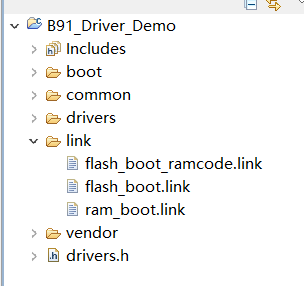

link

This folder is used to store link files and is selected according to different usage needs.

vendor

This folder is for the demo of all modules.

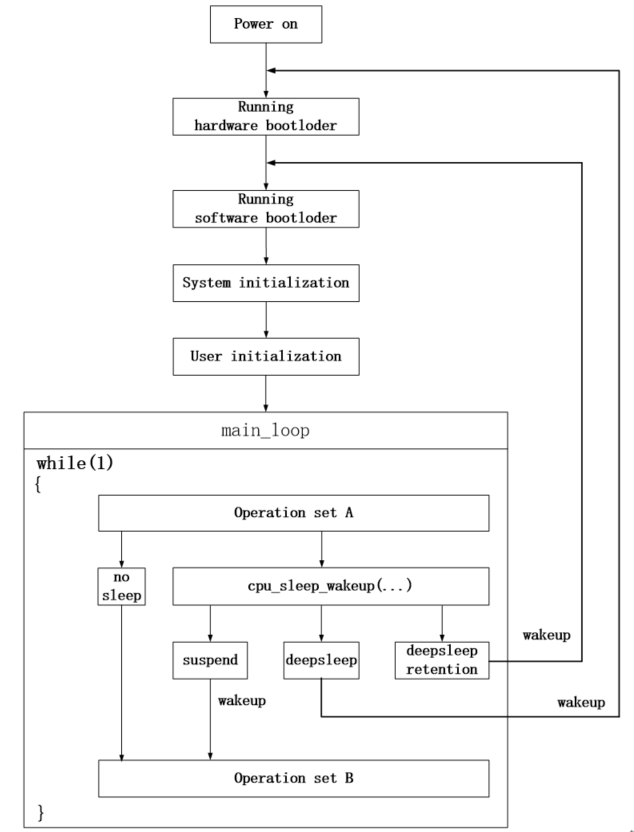

Boot mechanism

Telink platform SoC

a) Chip power on or wake up from deep mode: it will move a program from flash to RAM first, and then boot from RAM.

b) It boots directly from RAM after retention.

As you can see, the boot location here is the same, both are RAM.

Risc-V platform SoC

a) Chip power on or wake up from deep mode: Instead of moving the code from flash to RAM, it jumps to the start address of flash (0x20000000) and starts execution. (The reason why it can be handled in this way is that the chips of this series support taking commands directly from flash for execution.)

b) It will boot from IRAM after wake up from retention.

Note:

- There are two RAMs, one is IRAM and the other is DRAM, IRAM stores programs and data, DRAM can only store data.

As you can see, the boot location here is different. Two segments are in the link and S files, vectors and retention_reset segment, where the vector segment is at the flash start address and the retention segment is at the start of IRAM, which are both the boot code section. The code section will be handled differently, which will be explained in detail later.

S and link files

Use of combinations

According to different usage scenarios, we can choose the corresponding combination.

| Usage scenario | S file | link file |

|---|---|---|

| Common boot from flash | cstartup_b91_flash.S | flash_boot.link |

| Used when testing performance (coremark and dhrystone) | cstartup_b91_flash.S | flash_boot_ramcode.link |

| Used to load to ram to start the program, cannot be loadedto the flash for execution | cstartup_b91_ram.S | ram_boot.link |

The differences in the S files therein are as follows:

| S file | Description |

|---|---|

| cstartup_b91_flash.S | It is the S file required to start the program from flash. |

| cstartup_b91_ram.S | It is the S file required to start the program from ram. |

The differences in link files are as follows:

| link文件 | Description |

|---|---|

| flash_boot.link | Used in normal usage scenarios. |

| flash_boot_ramcode.link | The only difference with the flash_boot.link file is that it puts all the segments except the vector segment needed for booting into the ramcode segment, and all the programs run in ram, which makes the execution time fast. |

| ram_boot.link | This file is used to load to ram to start the program, cannot be loaded to flash for execution. This link file works with cstartup_b91_ram.S file. |

Configuration method

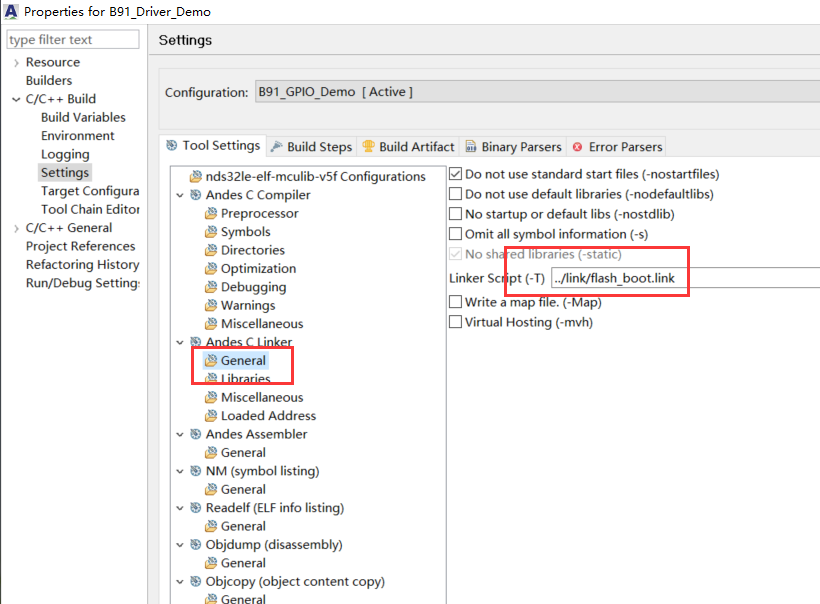

Link

You can select the link file to be used by the following configuration.

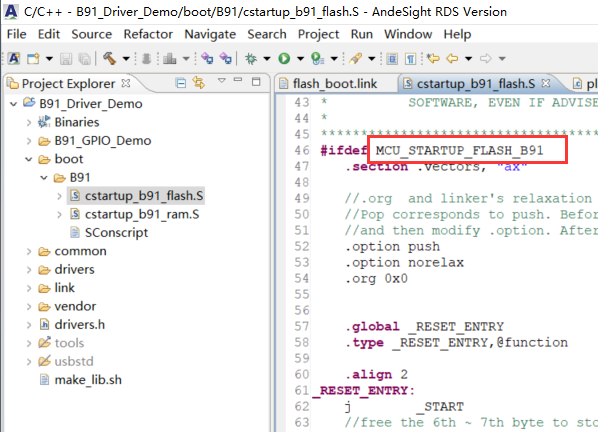

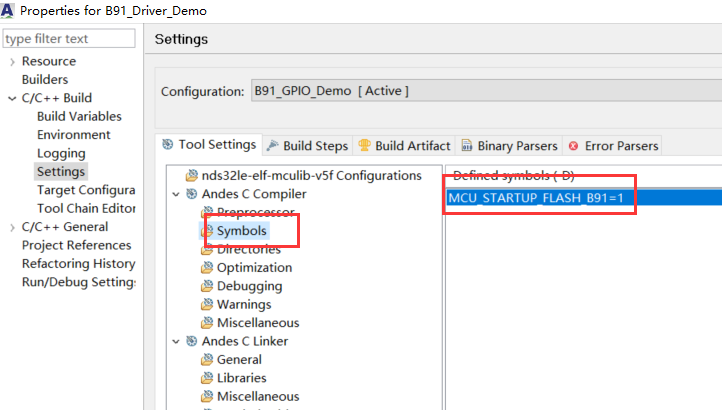

S file

S files are selected differently by the following macro definitions.

Macros can be defined in the following way to decide which S file to choose to use.

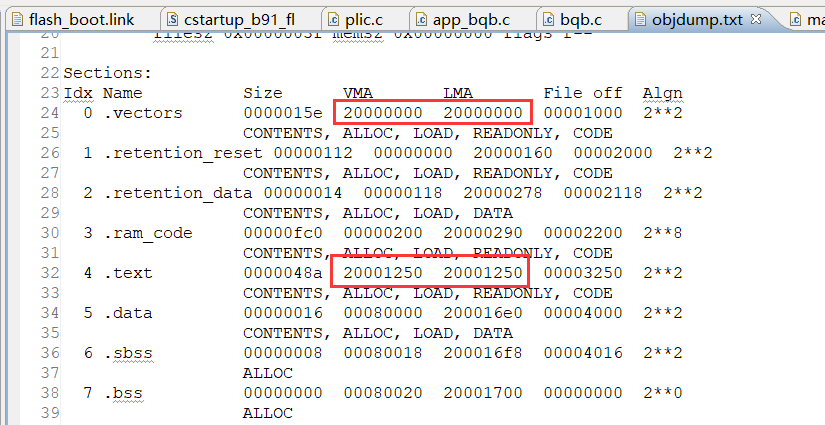

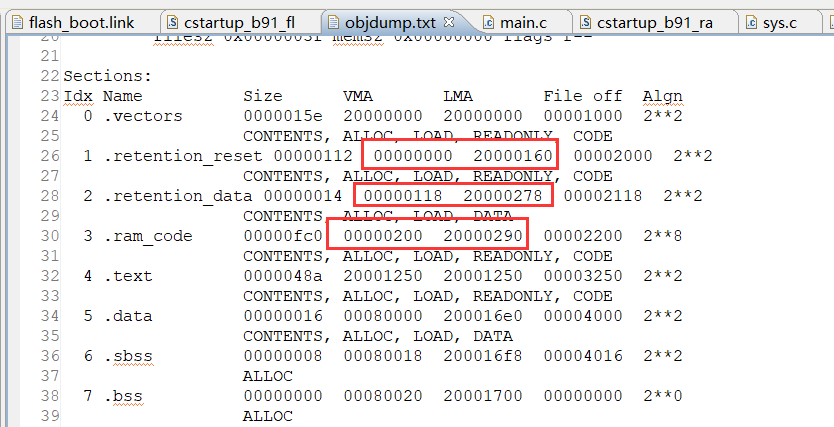

objdump.txt

The relevant distributions of VMA and LMA can be seen in the generated objdump.txt file.

The following figure shows an objdump.txt file generated by compiling with cstartup_b91_flash.S and flash_boot.link file.

In this file, the VMA and LMA addresses of vectors and text are the same, and these two segments are taken from the flash for execution.

The VMA and LMA addresses of retention_reset, retention_data, and ram_code are different. The LMA address is the flash address, and the VMA address is the IRAM address. In the S file, it will move these three segments from the flash to the IRAM correspondingly.

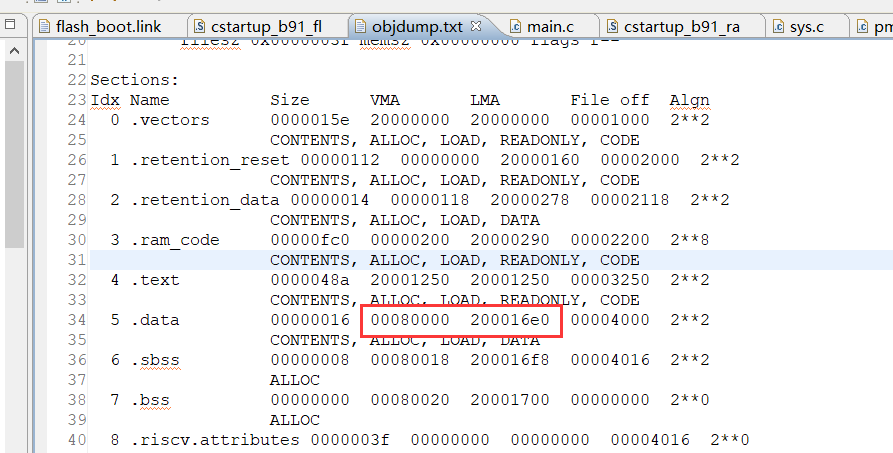

The addresses of VMA and LMA of data segment are different, the address of LMA is in flash and the address of VMA is in DRAM.

In the S file, the data segment will be moved from flash to DRAM correspondingly.

Link file details

Code detail

Take the flash_boot.link file as an example:

// Set the code entry to _RESET_ENTRY

ENTRY(_RESET_ENTRY)

SECTIONS

{

// Define the variable NDS_SAG_LMA_FLASH = 0x20000000

NDS_SAG_LMA_FLASH = 0x20000000 ;

//specify the current address is 0x20000000 (without AT addresses involved are VMA), the point is to represent the current address

//VMA(Virtual Memory Address): is the address where the program is running.

//LMA(Load Memory Address): The load address, here can be simply understood as the address in flash.

. = 0x20000000;

// Define the variable BIN_BEGIN equal to the current address

PROVIDE (BIN_BEGIN = .) .

// Define vectors segment, VMA address and LMA address are 0x2000000, so no AT commands are added here.

// that is, the vectors segment is loaded and run at 0x20000000 (here 0x20000000 is the base address of the flash, that is, vectors segment is stored in the flash 0x20000000, and also from this address to take the commands to run)

//keep is equivalent to telling the compiler that this section should not be garbage collected. The garbage collection is to remove unused sections and not output to the output file, set with the --gc-sections option. But you can use KEEP to keep it. For example, the following vectors section is required to be kept.

.vectors : { KEEP(*(.vectors )) }

//Specify the current location as 0x0 (which is the starting address of IRAM)

. = 0x00000000;

//Define the retention_reset segment with VMA address 0x0

//LMA address= ALIGN(LOADADADDR (.vectors) + SIZEOF (.vectors),8)

//LOADADDR (section): Get the address of the LMA of the section.

//SIZEOF (section): Get the size of the section

//AT (addr): Define the address of the LMA of this segment.

// When VMA and LMA do not match, you need to set LMA with AT commands

.retention_reset : AT( ALIGN(LOADADDR (.vectors) + SIZEOF (.vectors),8))

{ KEEP(*(.retention_reset )) }

// some addresses of retention_reset segment of VMA, LMA need to be saved to the variable, S file will be used.

PROVIDE (_RETENTION_RESET_VMA_START = ADDR(.retention_reset));

PROVIDE (_RETENTION_RESET_LMA_START = LOADADADDR(.retention_reset));

PROVIDE (_RETENTION_RESET_VMA_END = .) .

//The aes_data segment can be only in the first 64K addresses of the IRAM, so please do not modify its location if you are not sure of the usage.

// Set current address = . Address aligned by 8

// If no value (point) is assigned to the current address, the addresses of all segments will be listed in order.

. = ALIGN(8);

PROVIDE (_AES_VMA_START = .) .

.aes_data (NOLOAD) : { KEEP(*(.aes_data )) }

PROVIDE (_AES_VMA_END = .) .

. = ALIGN(8);

.retention_data : AT( ALIGN(LOADADDR (.retention_reset) + SIZEOF (.retention_reset),8))

{ KEEP(*(.retention_data )) }

PROVIDE (_RETENTION_DATA_VMA_START = ADDR(.retention_data));

PROVIDE (_RETENTION_DATA_LMA_START = LOADADADDR(.retention_data));

PROVIDE (_RETENTION_DATA_VMA_END = .) .

. = ALIGN(8);

.ram_code : AT( ALIGN(LOADADDR (.retention_data) + SIZEOF (.retention_data),8))

{ KEEP(*(.ram_code )) }

PROVIDE (_RAMCODE_VMA_END = .) .

PROVIDE (_RAMCODE_VMA_START = ADDR(.ram_code));

PROVIDE (_RAMCODE_LMA_START = LOADADADDR(.ram_code));

PROVIDE (_RAMCODE_SIZE = SIZEOF (.ram_code));

. = ALIGN(LOADADADDR (.ram_code) + SIZEOF (.ram_code), 8);

.text : AT(ALIGN(LOADADADDR (.ram_code) + SIZEOF (.ram_code), 8))

{ *(.text .stub .text.* .gnu.linkonce.t.* ) KEEP(*(.text.*personality* )) *(.gnu.warning ) }

. rodata : AT(ALIGN(LOADADADDR (.text) + SIZEOF (.text), ALIGNOF(. rodata)))

{ *(. rodata . rodata.* .gnu.linkonce.r.* )}

//Added allocation of segments of eh_frame/eh_frame_hdr, compile error will occur if there is no allocation when using puts function

.eh_frame_hdr : AT(ALIGN(LOADADADDR (. rodata) + SIZEOF (. rodata), ALIGNOF(.eh_frame_hdr)))

{ *(.eh_frame_hdr ) }

. = ALIGN(0x20);

.eh_frame : AT(ALIGN(LOADADDR (.eh_frame_hdr) + SIZEOF (.eh_frame_hdr), 32))

{ KEEP(*(.eh_frame )) }

//allocate memory space for the command compression table.exec.itable

.exec.itable : AT(ALIGN(LOADADDR (.eh_frame) + SIZEOF (.eh_frame), ALIGNOF(.exec.itable)))

{ KEEP(*(.exec.itable)) }

. = 0x00080000;

PROVIDE( __global_pointer$ = . + (4K / 2) );

// ALIGNOF(.data): return the alignment requirement of the VMA of data.

// If the section has been allocated, it will return the aligned byte named “section”. The linker will report an error if the section has not been allocated yet.

.data : AT(ALIGN(LOADADADDR (.exec.itable) + SIZEOF (.exec.itable), ALIGNOF(.data)))

{ *(.data .data.* .gnu.linkonce.d.* ) KEEP(*(.gnu.linkonce.d.*personality* )) SORT(CONSTRUCTORS)

\*(.srodata.cst16 ) \*(.srodata.cst8 ) \*(.srodata.cst4 ) \*(.srodata.cst2 ) \*(. srodata . srodata.\* ) \*(. sdata . sdata.\* .gnu.linkonce.s.\* ) \*(.sdata2 .sdata2.\* .gnu.linkonce.s.\* )

}

PROVIDE (_DATA_VMA_END = .) .

PROVIDE (_DATA_VMA_START = ADDR(.data));

PROVIDE (_DATA_LMA_START = LOADADDR(.data));

//BIN_SIZE = LMA address of data segment + size of data segment - BIN_BEGIN.

//The bin file is actually the LMA of all the segments stitched together and generally arranged in order (the values in the AT commands are set according to this rule)

PROVIDE (BIN_SIZE = LOADADDR(.data) + SIZEOF(.data) - BIN_BEGIN);

//Each output section can have a type, and the type is a keyword enclosed in parentheses.

// NOLOAD, section is marked as a non-loadable type and will not be loaded into memory when the program runs.

//The bss segment does not need to be loaded, the S file will zero out the VMA address space of the bss segment.

. = ALIGN(8);

PROVIDE (_BSS_VMA_START = .) .

. sbss (NOLOAD) : { \*(. dynsbss ) \*(. sbss . sbss.\* .gnu.linkonce.sb.* ) \*(. scommon . scommon.\* ) }

. bss (NOLOAD) : { \*(. dynbss ) \*(. bss . bss.\* .gnu.linkonce.b.\* ) \*(COMMON ) . = ALIGN(8); }

PROVIDE (_BSS_VMA_END = .) .

. = ALIGN(8);

//_end is the starting address of the heap, the heap is growing upwards, and generally we set it in the space not used after bss

// functions like sprintf/malloc/free are called, these functions will call the _sbrk function to allocate heap memory, and _sbrk will determine where to start allocating heap space via the _end symbol (usually the end of the .bss segment), otherwise a link error will occur.

_end = .

PROVIDE (end = .) .

//Define the start address of the stack, here the end location of DRAM is defined.

PROVIDE (_STACK_TOP = 0x00a0000);

PROVIDE (FLASH_SIZE = 0x0100000);

}

ASSERT((BIN_SIZE)<= FLASH_SIZE, "BIN FILE OVERFLOW");

Alignment

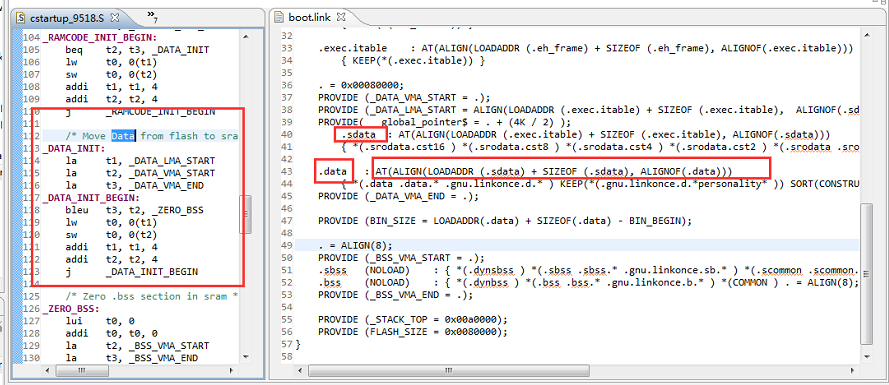

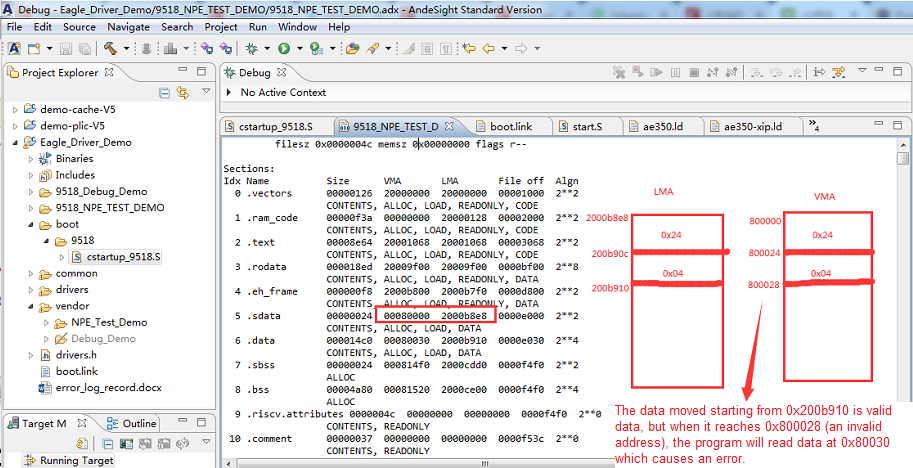

The link file involves some alignment rules. If it involves multiple segments moved together, you need to pay attention to the alignment of these segments. When the starting address of LMA and VMA are not consistent, multiple segments moving together is likely to encounter move error.

The following is an example of an error:

The code in the S file is trying to move the sdata and data segments from the LMA to the VMA. The starting address of the VMA is 0x00080000 and the starting address of the LMA is related to the previous code and is aligned according to the alignment rules of the VMA for sdata.

The following figure shows an error-prone lst file compiled with the above link file.

There are several methods of modification:

(1) Move one segment at a time so that you don't have the problems above.

(2) Merge sdata, data segments.

S file details

Take the cstartup_b91_flash.S file as an example.

Code detail

// Define the vector segment, the code starting after this sentence belongs to the vectors segment, until the next segment name encountered, or the end of the file

// where "ax" means the section is assignable and executable

//`a' section is allocable `x' section is executable

.section .vectors, "ax"

.option push //push saves the current .option configuration

.option norelax //set to norelax

.org 0x0 //The pseudo command .org is telling the compiler the offset address of the next command. Set the offset address to 0.

//The .global pseudo-command is used to define a global symbol that allows the linker to recognize it globally, that is a symbol defined in a program file can be visible to all other program files.

.global _RESET_ENTRY

// The .type pseudo-command is used to define the type of the symbol. The following is the definition of _RESET_ENTRY as a function

.type _RESET_ENTRY,@function

// The .align pseudo-command is used to push the current PC address to a location aligned to "the integer power of 2 bytes". The following is to push the current PC address to 4 bytes aligned.

.align 2

//The label _RESET_ENTRY is the entry address of the program.

_RESET_ENTRY:

//The entry address of the program must be an executable command, here is a jump command to the label _START

j _START

// Set the offset address to 0x18 to store BIN_SIZE (4 bytes), BIN_SIZE is defined in the link file.

.org 0x18

.word (BIN_SIZE)

// Set the offset address to 0x20 to store the keyword, this location must be this value, otherwise the program will not run.

.org 0x20

.word ('T'<<24 | 'L'<<16 | 'N'<<8 | 'K')

// Set the offset address to 0x26 to store the flash configuration, later the flash fetching command will decide which protocol to go according to this configuration.

//The following 6 are supported and can be selected according to flash model.

.org 0x26

//.short (0x0003) //READ: cmd:1x, addr:1x, data:1x, dummy:0

//.short (0x070B) //FREAD: cmd:1x, addr:1x, data:1x, dummy:8

.short (0x173B) //DREAD: cmd:1x, addr:1x, data:2x, dummy:8

//.short (0x53BB) //X2READ: cmd:1x, addr:2x, data:2x, dummy:4

//.short (0x276B) //QREAD: cmd:1x, addr:1x, data:4x, dummy:8

//.short (0x65EB) //X4READ: cmd:1x, addr:4x, data:4x, dummy:6

// Use pop to restore .option configuration

.option pop

//4 byte alignment

.align 2

_START:

//This is for debug use, it will output PB4 high. It is generally used to check the status, the default is off.

#if 0

lui t0,0x80140 //0x8014030a

li t1, 0xef

li t2, 0x10

sb t1 , 0x30a(t0) //0x8014030a PB oen = 0xef

sb t2 , 0x30b(t0) //0x8014030b PB output = 0x10

#endif

//initialize the global pointer gp register, __global_pointer$ is defined in the link file.

.option push

.option norelax

la gp, __global_pointer$

.option pop

//initialize stack pointer sp register, _STACK_TOP is defined in the link file.

la t0, _STACK_TOP

mv sp, t0

#ifdef __nds_execit

// Set the command compression table and address

la t0, _ITB_BASE_

csrw uitb , t0

#endif

// Set FS to 0b11, clear fscsr (is the processing that needs to be done before floating point operations)

#ifdef __riscv_flen

/* Enable FPU */

li t0, 0x00006000

csrrs t0, mstatus , t0

/* Initialize FCSR */

fscsr zero

#endif

// Set the interrupt entry base address

la t0, __vectors

csrw mtvec, t0

// enable interrupt vector mode (need to enable two places, no modification here)

/* Enable vectored external plic interrupt */

csrsi mmisc_ctl, 2

/*vector mode enable bit (VECTORED) of the Feature Enable Register */

lui t0, 0xe4000

li t1, 0x02

sw t1, 0x0(t0) //(*(volatile unsigned long*)(0xe4000000))= 0x02

// Enable I/D-Cache

csrr t0, mcache_ctl

ori t0, t0, 1 #/I-Cache

ori t0, t0, 2 #/D-Cache

csrw mcache_ctl, t0

fence.i

//Move the retention_reset segment from flash to ram

_RETENTION_RESET_INIT:

la t1, _RETENTION_RESET_LMA_START

la t2, _RETENTION_RESET_VMA_START

la t3, _RETENTION_RESET_VMA_END

_RETENTION_RESET_BEGIN:

bleu t3, t2, _RETENTION_DATA_INIT

lw t0, 0(t1)

sw t0, 0(t2)

addi t1, t1, 4

addi t2, t2, 4

j _RETENTION_RESET_BEGIN

//Move the retention_data segment from flash to ram

_RETENTION_DATA_INIT:

la t1, _RETENTION_DATA_LMA_START

la t2, _RETENTION_DATA_VMA_START

la t3, _RETENTION_DATA_VMA_END

_RETENTION_DATA_INIT_BEGIN:

bleu t3, t2, _RAMCODE_INIT

lw t0, 0(t1)

sw t0, 0(t2)

addi t1, t1, 4

addi t2, t2, 4

j _RETENTION_DATA_INIT_BEGIN

//Move ram_code segment from flash to ram

_RAMCODE_INIT:

la t1, _RAMCODE_LMA_START

la t2, _RAMCODE_VMA_START

la t3, _RAMCODE_VMA_END

_RAMCODE_INIT_BEGIN:

bleu t3, t2, _DATA_INIT

lw t0, 0(t1)

sw t0, 0(t2)

addi t1, t1, 4

addi t2, t2, 4

j _RAMCODE_INIT_BEGIN

//Move data segments from flash to ram

_DATA_INIT:

la t1, _DATA_LMA_START

la t2, _DATA_VMA_START

la t3, _DATA_VMA_END

_DATA_INIT_BEGIN:

bleu t3, t2, _ZERO_BSS

lw t0, 0(t1)

sw t0, 0(t2)

addi t1, t1, 4

addi t2, t2, 4

j _DATA_INIT_BEGIN

//clear the bss segment to zero

_ZERO_BSS:

lui t0, 0

la t2, _BSS_VMA_START

la t3, _BSS_VMA_END

_ZERO_BSS_BEGIN:

bleu t3, t2, _ZERO_AES

sw t0, 0(t2)

addi t2, t2, 4

j _ZERO_BSS_BEGIN

// Clear the AES segment to zero

_ZERO_AES:

lui t0, 0

la t2, _AES_VMA_START

la t3, _AES_VMA_END

_ZERO_AES_BEGIN:

bleu t3, t2, _FILL_STK

sw t0, 0(t2)

addi t2, t2, 4

j _ZERO_AES_BEGIN

//The stack area are initialized to 0x55, the default code is not open, because the ram is relatively large and will be more time-consuming. If the debug needs, it can be opened to use.

_FILL_STK:

#if 0

lui t0, 0x55555

addi t0, t0, 0x555

la t2, _BSS_VMA_END

la t3, _STACK_TOP

_FILL_STK_BEGIN:

bleu t3, t2, _MAIN_FUNC

sw t0, 0(t2)

addi t2, t2, 4

j _FILL_STK_BEGIN

#endif

//jump to the main function

_MAIN_FUNC:

nop

//Use j or jal can only jump to [-524288,524287], beyond this range we can only use jalr to achieve, in order to avoid such problems, we uniformly use jalr to jump.

la t0, main

jalr t0

nop

nop

nop

nop

nop

_END:

j _END

//Define a macro with the name INTERRUPT, the parameter is num, and the macro ends at .endm

.macro INTERRUPT num

//Weak definition

.weak entry_irq\num

.set entry_irq\num, default_irq_entry

.long entry_irq\num

.endm

//There are a total of 64 interrupt sources

#define VECTOR_NUMINTRS 63

.section .ram_code, "ax"

//Define ram_code segment, all interrupt entry address should be in ram_code, so as to enter interrupt quickly.

.global __vectors

// There are 64 interrupt sources, and the formula for the alignment that needs to be set here is: 2ceiling(log2(N))+2, and N is 64, so the it should be set to 256 alignment here.

.balign 256

__vectors:

.long trap_entry

//Actually here is a for loop that defines the 63 interrupt entry addresses in addition to the trap interrupt.

//after expansion is:

//.weak entry_irq1

//.set entry_irq1, default_irq_entry

//.long entry_irq1

//.........

//.weak entry_irq63

//.set entry_irq63, default_irq_entry

//.long entry_irq63

//We use vector mode, after an interrupt occurs, the pc will point to address __vectors +4*interrupt ID, if the interrupt ID is 2, it will jump to entry_irq2

.altmacro

.set irqno, 1

.rept VECTOR_NUMINTRS/* .rept .endr */

INTERRUPT %irqno

.set irqno, irqno+1

.endr

Differences between vectors and retention_reset segments

The retention_reset is the startup code that will run when comes back from retention.

The current retention_reset processing is not to move these segments (retention_reset, retention_data, ram_code) from flash to ram, because these segments are retained during the retention phase and will not be lost. The condition for this processing is that the size of the retention ram is larger than these segments, and if there is more than that, then the move action needs to be done.

The retention_reset boot part requires more processing than the vectors, include: flash wake-up, multi-address register recovery. which is a must-do processing coming from the retention.

Others

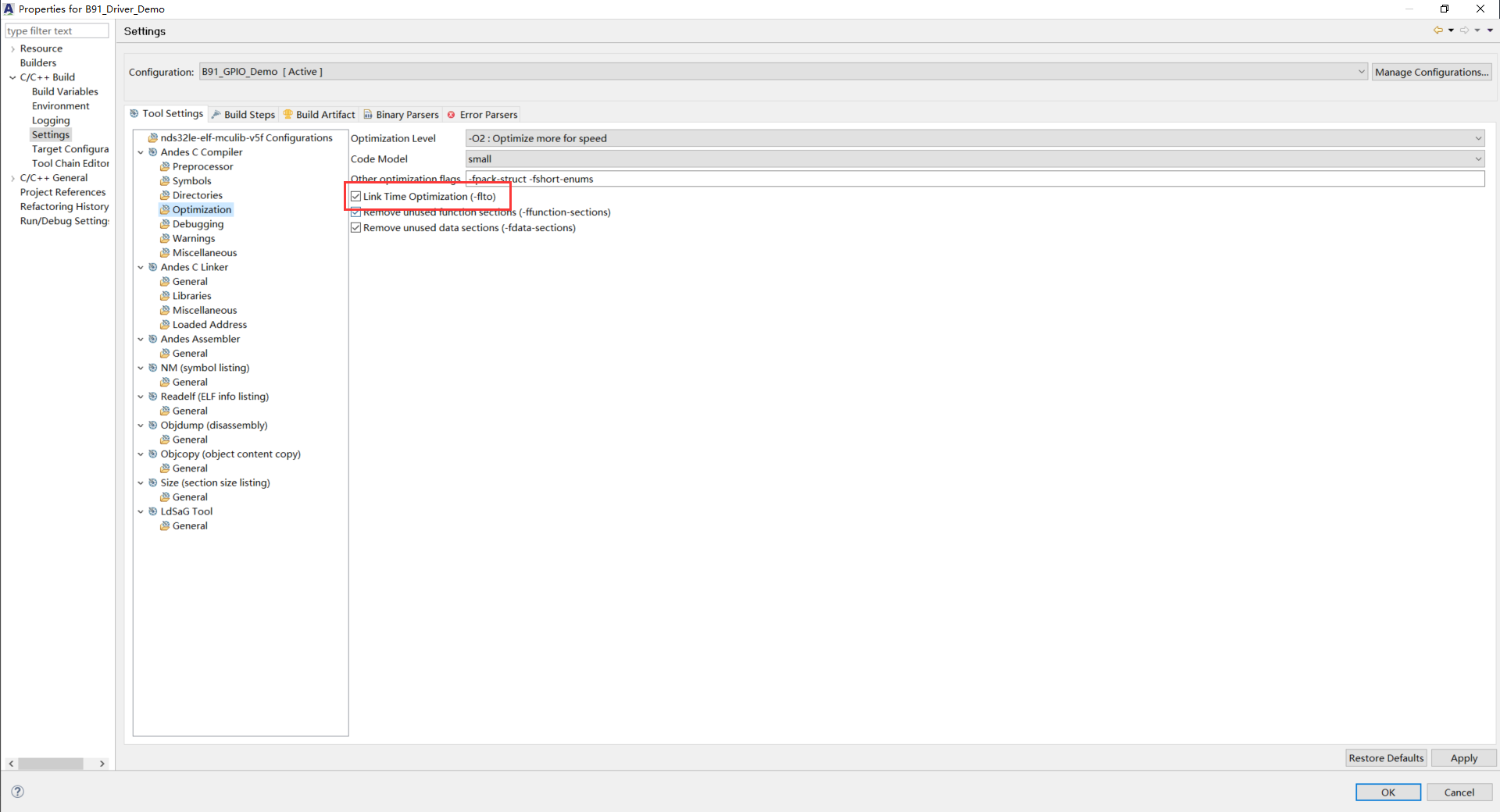

(1) Notes on the use of .org

In the current compilation environment, .org and Link Time Optimization (-flto) in the optimization option cannot be used at the same time. However, (-flto) is definitely selected in order to compile a small bin file, so if you want to use .org in the S file, you need to use it as follows:

.option push //push saves the current .option configuration

.option norelax // set to norelax

.org 0x0 //set .org

.........

.option pop // Use pop to restore the .option configuration

The description of .option is as follows:

The .option pseudo-command is used to set certain architecture-specific options that enable the assembler to recognize the option and act according to the definition of the option.

The push, pop are used to temporarily save or restore the options specified by the .option pseudo-command:

The ".option push" pseudo-command temporarily saves the current option settings, allowing new options to be specified later using the .option pseudo-command, while the ".option pop" pseudo-command restores the most recently saved option settings to take effect again.

The combination of ".option push" and ".option pop" makes it possible to set different options specifically for a section of code embedded in an assembly program without affecting the global option settings.

(2) Compression command

The RISC-V's C Extension, which refers to replacing 32bit commands with 16bit commands, and Andes' CoDense (Code Dense) technology puts 32bit commands inside the command table and replaces them with 16 EXEC.IT 0xxxxx where the original 32bit commands appear.

The macro _nds_execit is set to be on by compiler default, while _ITB_BASE will be set to the first address of .exec.itable.

Set ITB_BASE to register uitb in the S file as the base address of the command table. The compression instructions are put into the .exec.itable segment.

(3) FPU enable

The macro __riscv_flen is set to be on by compiler default.

Before executing a floating-point command, the mstatus<14:13> FS segment needs to be changed to a non-zero value, otherwise a command exception will occur. So the S file sets FS to 0b11 and initializes the floating-point control status register FCSR to 0.

Debug Demo

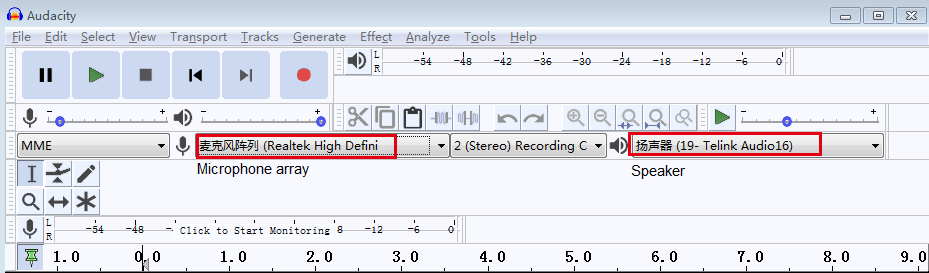

The driver does not redefine the printf interface, it directly uses the printf interface that comes with toolchain. However, we redirect it, the driver implements two kinds of redirection, one is to redirect the data to GPIO (through GPIO to simulate serial timing), the other one is to redirect to USB. You can choose either one for debug info output.

You can choose whether to use GPIO or USB printing in printf.h.

#define DEBUG_IO 0

#define DEBUG_USB 1

#define DEBUG_BUS DEBUG_IO

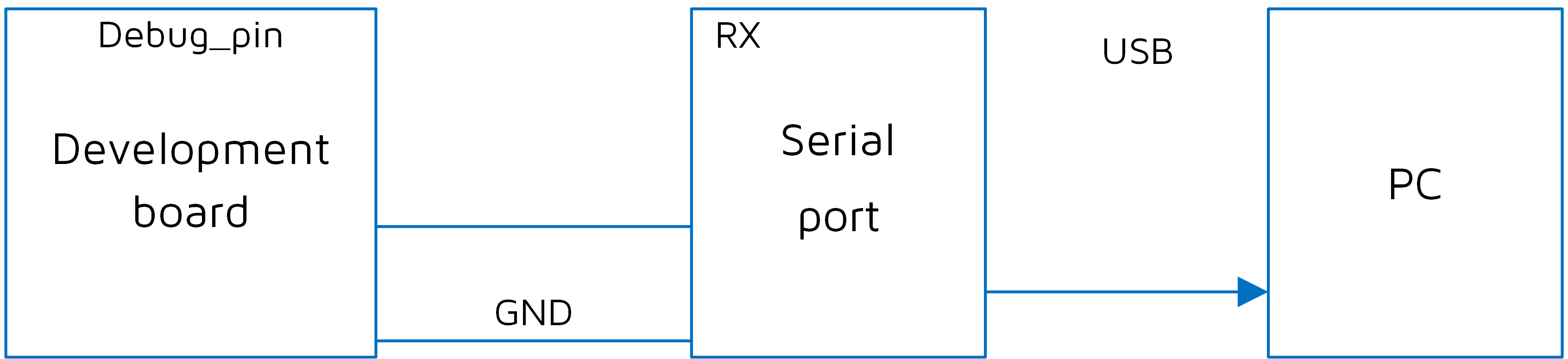

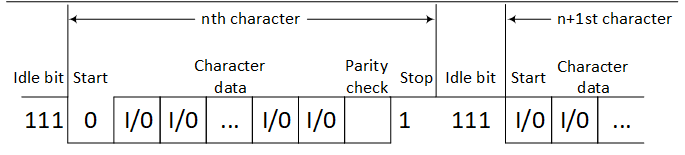

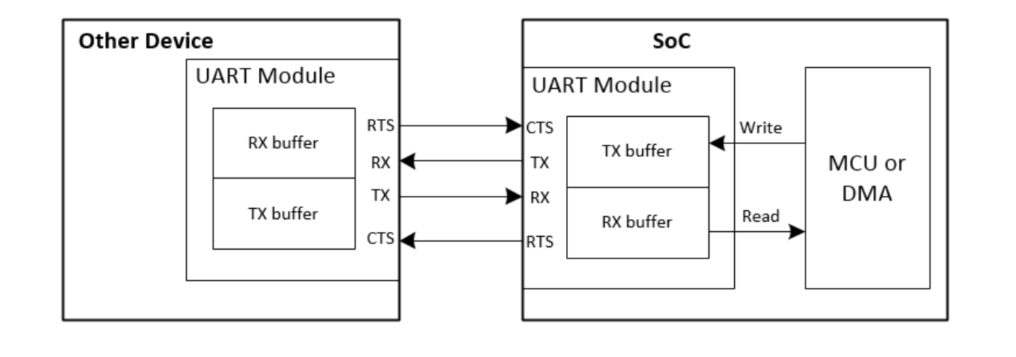

Simulate serial output via GPIO port

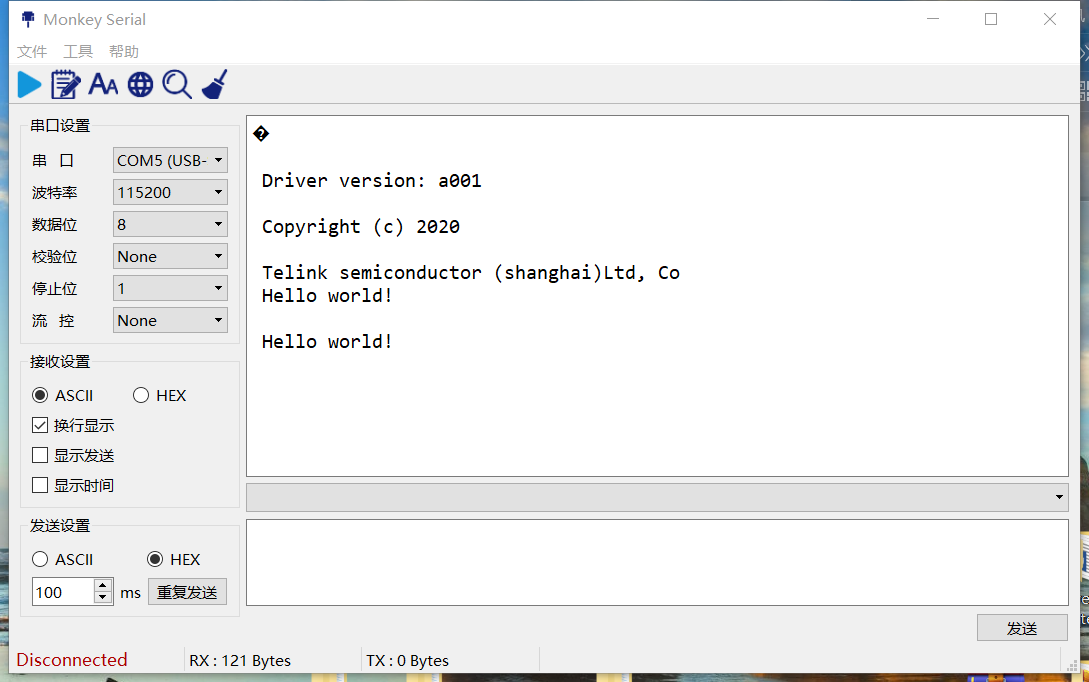

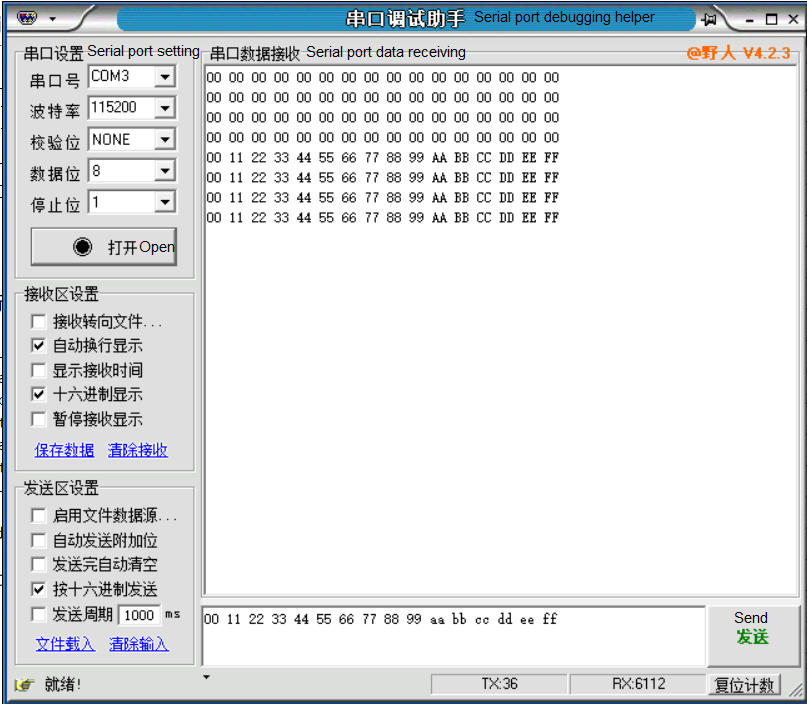

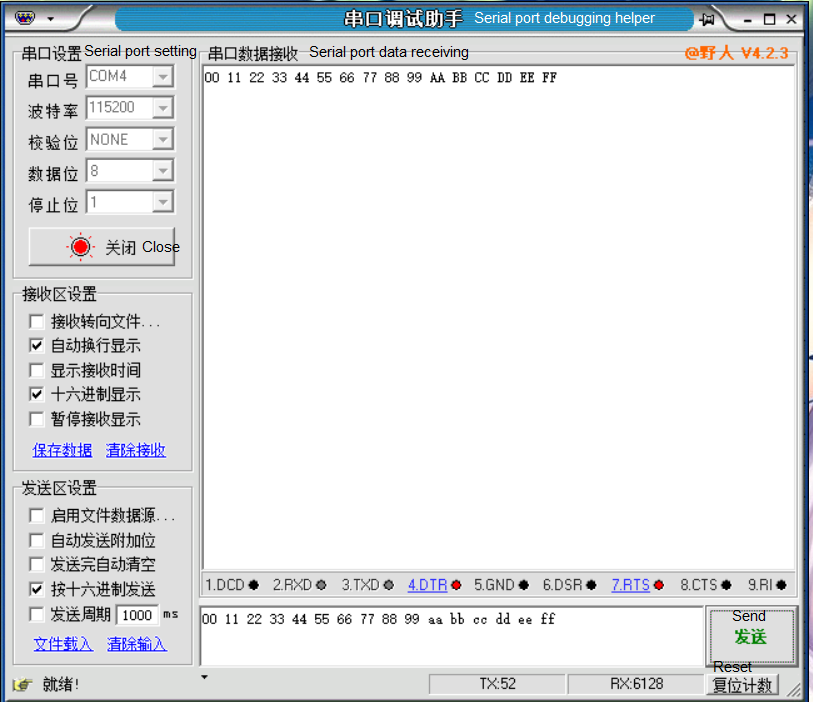

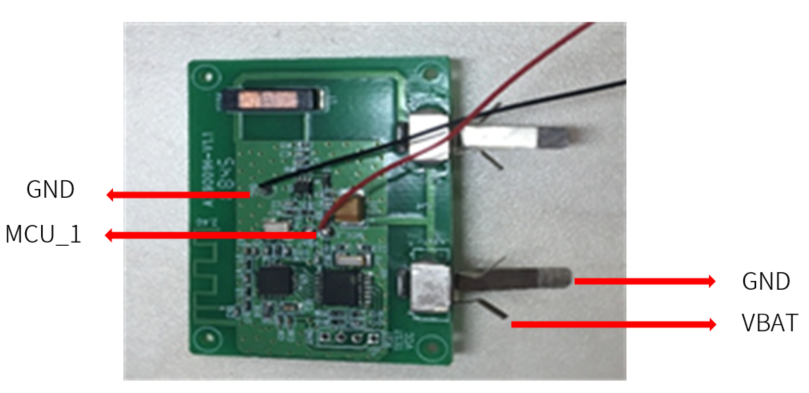

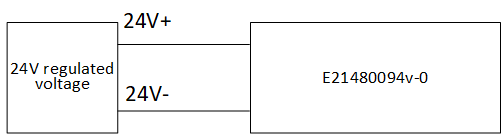

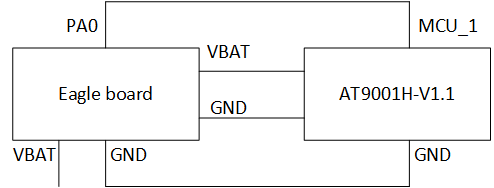

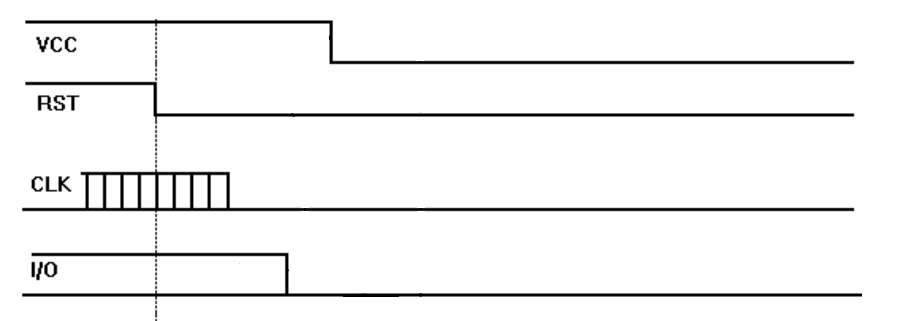

GPIO port related configuration is configured in printf.h, including baud rate, and others (only RX and GND need to be connected). The hardware connections are as follows:

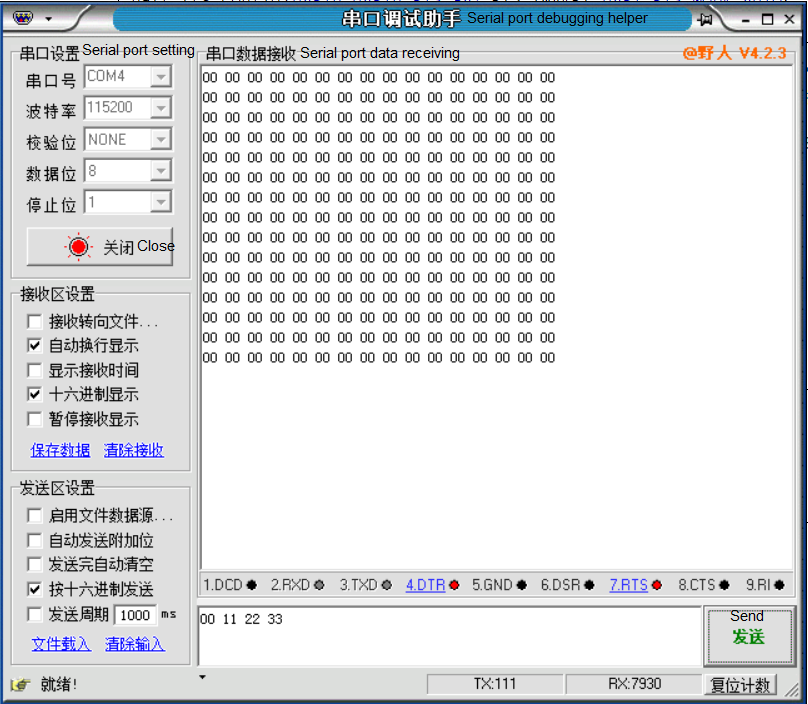

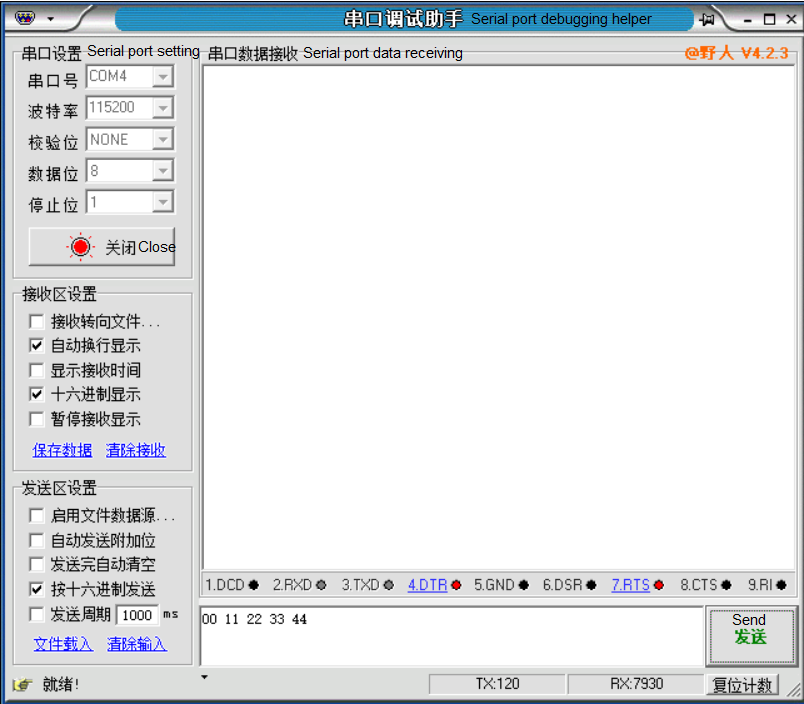

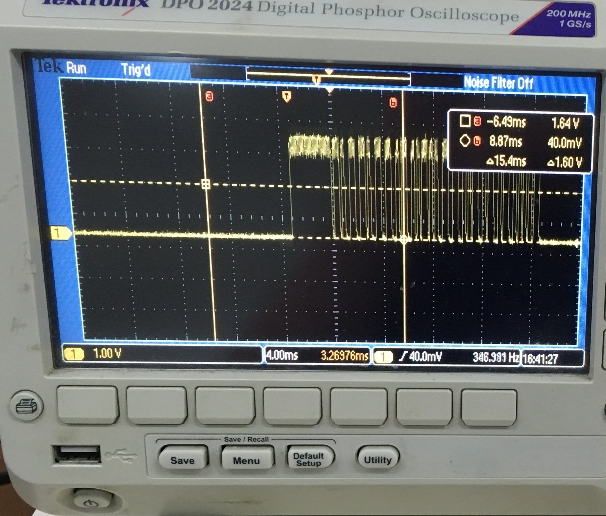

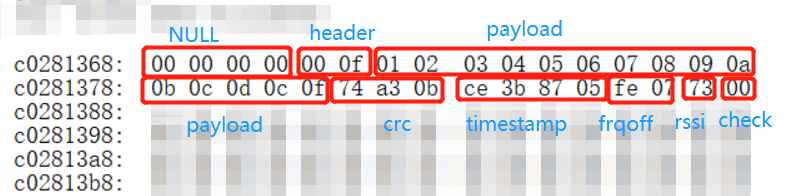

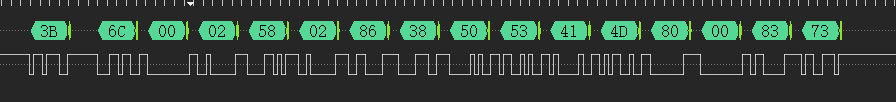

The following figure shows the printout received by the serial assistant tool:

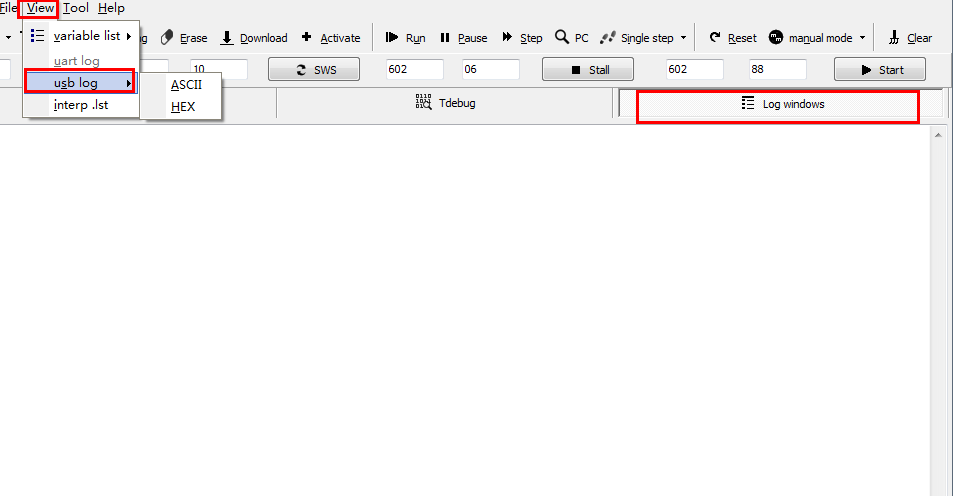

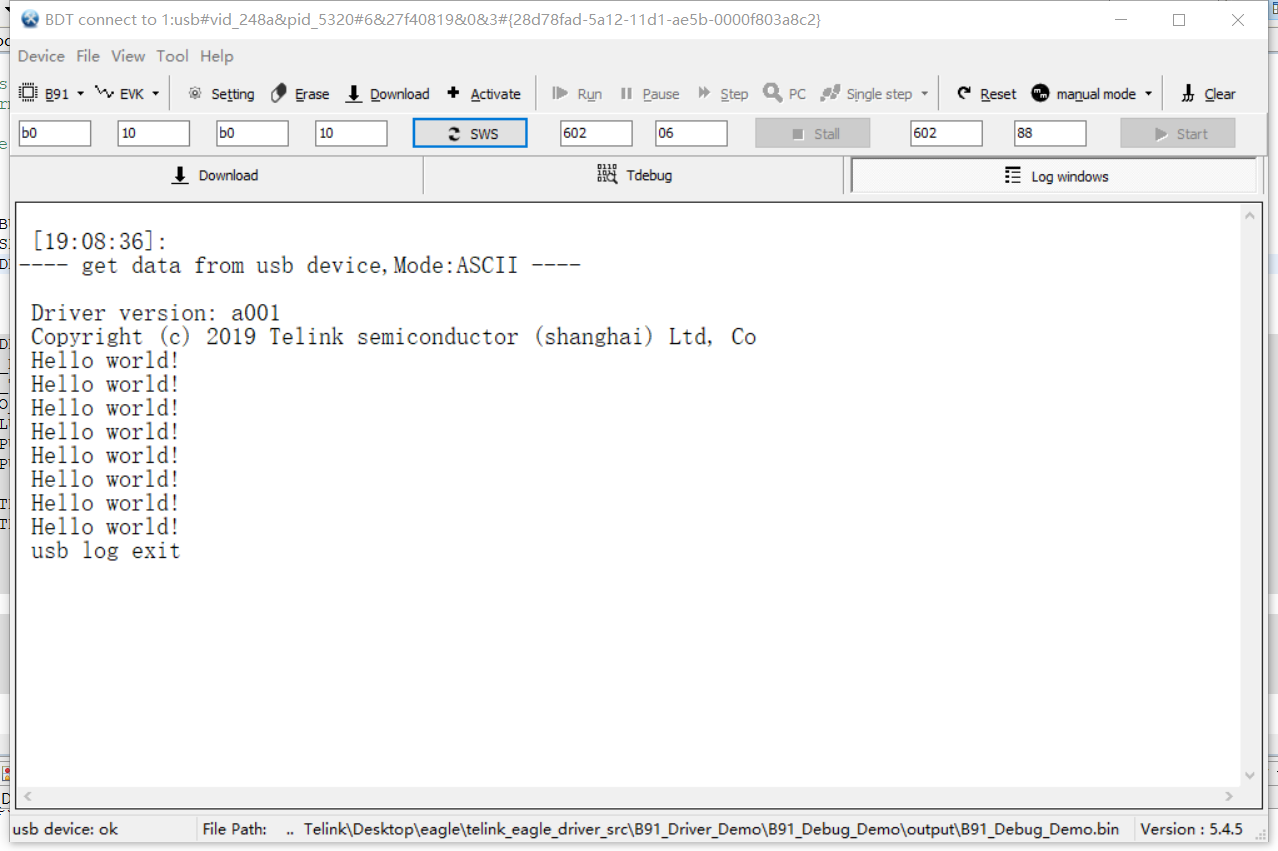

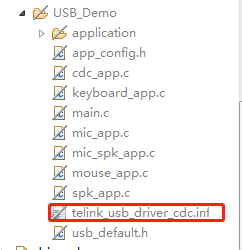

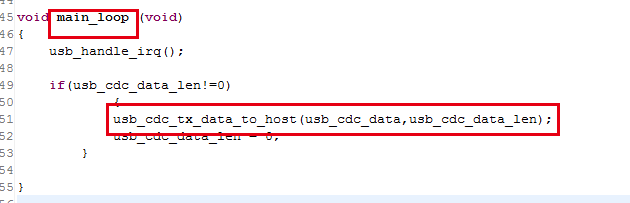

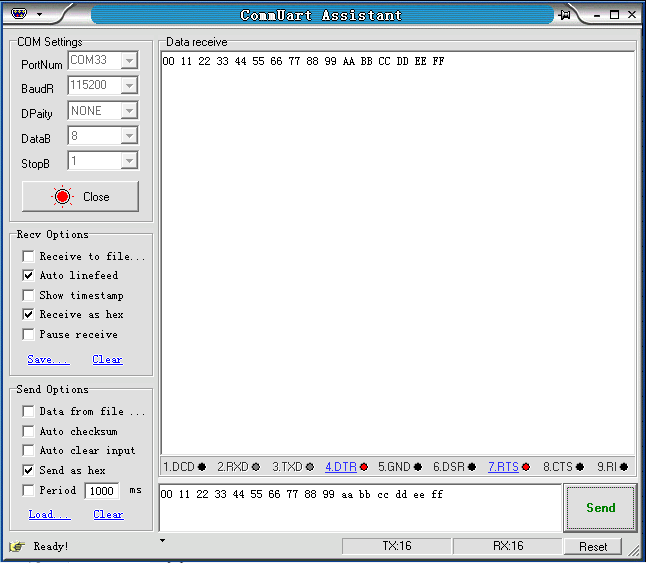

USB printout

Configuring USB printf, you need to use the BDT tool to view the output information. The point to note when using USB printf is that the USB uses a fixed 48M clock, in the clock initialization it is configured by default. However, if the PLL clock used cannot be divided to get 48M, then the USB may not work properly.

When using USB printf, you can configure blocking and non-blocking modes, which can be selected through the relevant macro definitions in printf. The default is non-blocking as follows:

#define BLOCK_MODE 0

The following is the BDT configuring usb_log method and experimental phenomena:

Interrupt

The PLIC (Platform-Level Interrupt Controller) is compatible with RISC-V PLIC and has two major functions: interrupt vector and interrupt priority.

Interrupt overview

In the interrupt mechanism, the processor is suddenly interrupted by another request during the sequential execution of the program command stream and aborts the execution of the current program to deal with something else. After it has finished processing something else, it then reverts to the point where the program was interrupted to continue executing the previous program command stream. The "other request" is called an interrupt request, and the other "request source" is called the interrupt source, which usually comes from a peripheral device. The processor turns to perform "something else", which is called an interrupt processing program.

Interrupt type

The RISV-V architecture has three modes of operation: Machine Mode, User Mode and Supervisor Mode. We are using Machine Mode, and there are three types of interrupts in Machine Mode: Software Interrupt, Timer Interrupt, and External Interrupt. The external interrupt refers to CPU external interrupts, such as from UART, GPIO, and so on; the timer interrupt refers to interrupts from timers; the software interrupt is an interrupt triggered by the software itself.

Note:

- There are two modes of interrupt, vector and regular mode, and the driver defaults to vector mode.

External interrupt

Interrupt enable

For the use of the driver interrupt interface, if you want to open the interrupt, it has the following three levels:

The first layer

core_enable_interrupt()

It enables the corresponding BIT in the CSR register of the RISC-V core, which is the general interrupt switch.

Second layer

plic_interrupt_enable()

It enables the BIT of the corresponding module in the plic module, which is the module interrupt control switch.

Third layer

rf_set_irq_mask(FLD_ZB_RX_IRQ)

It enables the mask of the corresponding module, take the rf module as an example, set which one you need to use.

External interrupt handler function in vector mode

The corresponding interrupt handler functions have been defined in the plic driver and correspond to the following:

| Interrup vectors | Interrupt handler functions |

|---|---|

| IRQ0_EXCEPTION | except_handler |

| IRQ1_SYSTIMER | stimer_irq_handler |

| IRQ2_ALG | analog_irq_handler |

| IRQ3_TIMER1 | timer1_irq_handler |

| IRQ4_TIMER0 | timer0_irq_handler |

| IRQ5_DMA | dma_irq_handler |

| IRQ6_BMC | bmc_irq_handler |

| IRQ7_USB_CTRL_EP_SETUP | usb_ctrl_ep_setup_irq_handler |

| IRQ8_USB_CTRL_EP_DATA | usb_ctrl_ep_data_irq_handler |

| IRQ9_USB_CTRL_EP_STATUS | usb_ctrl_ep_status_irq_handler |

| IRQ10_USB_CTRL_EP_SETINF | usb_ctrl_ep_setinf_irq_handler |

| IRQ11_USB_ENDPOINT | usb_endpoint_irq_handler |

| IRQ12_ZB_DM | rf_dm_irq_handler |

| IRQ13_ZB_BLE | rf_ble_irq_handler |

| IRQ14_ZB_BT | rf_bt_irq_handler |

| IRQ15_ZB_RT | rf_irq_handler |

| IRQ16_PWM | pwm_irq_handler |

| IRQ17_PKE | pke_irq_handler |

| IRQ18_UART1 | uart1_irq_handler |

| IRQ19_UART0 | uart0_irq_handler |

| IRQ20_DFIFO | audio_irq_handler |

| IRQ21_I2C | i2c_irq_handler |

| IRQ22_SPI_AHB | hspi_irq_handler |

| IRQ23_SPI_APB | pspi_irq_handler |

| IRQ24_USB_PWDN | usb_pwdn_irq_handler |

| IRQ25_GPIO | gpio_irq_handler |

| IRQ26_GPIO2RISC0 | gpio_risc0_irq_handler |

| IRQ27_GPIO2RISC1 | gpio_risc1_irq_handler |

| IRQ28_SOFT | soft_irq_handler |

| IRQ29_NPE_BUS0 | npe_bus0_irq_handler |

| IRQ30_NPE_BUS1 | npe_bus1_irq_handler |

| IRQ31_NPE_BUS2 | npe_bus2_irq_handler |

| IRQ32_NPE_BUS3 | npe_bus3_irq_handler |

| IRQ33_NPE_BUS4 | npe_bus4_irq_handler |

| IRQ35_USB_RESET | usb_reset_irq_handler |

| IRQ36_NPE_BUS7 | npe_bus7_irq_handler |

| IRQ37_NPE_BUS8 | npe_bus8_irq_handler |

| IRQ42_NPE_BUS13 | npe_bus13_irq_handler |

| IRQ43_NPE_BUS14 | npe_bus14_irq_handler |

| IRQ44_NPE_BUS15 | npe_bus15_irq_handler |

| IRQ46_NPE_BUS17 | npe_bus17_irq_handler |

| IRQ50_NPE_BUS21 | npe_bus21_irq_handler |

| IRQ51_NPE_BUS22 | npe_bus22_irq_handler |

| IRQ52_NPE_BUS23 | npe_bus23_irq_handler |

| IRQ53_NPE_BUS24 | npe_bus24_irq_handler |

| IRQ54_NPE_BUS25 | npe_bus25_irq_handler |

| IRQ55_NPE_BUS26 | npe_bus26_irq_handler |

| IRQ56_NPE_BUS27 | npe_bus27_irq_handler |

| IRQ57_NPE_BUS28 | npe_bus28_irq_handler |

| IRQ58_NPE_BUS29 | npe_bus29_irq_handler |

| IRQ59_NPE_BUS30 | npe_bus30_irq_handler |

| IRQ60_NPE_BUS31 | npe_bus31_irq_handler |

| IRQ61_NPE_COMB | npe_comb_irq_handler |

| IRQ62_PM_TM | pm_irq_handler |

| IRQ63_EOC | eoc_irq_handler |

__attribute__((section(".ram_code"))) void default_irq_handler(void)

{

}

void stimer_irq_handler(void) __attribute__((weak, alias("default_irq_handler")));

By default, all interrupt handler functions are weakly defined as default_irq_handler, an empty function.

Weak function

In theory, a project is not allowed to have two functions with the same name. Here it is OK to use _weak to specify that one of them is a weak function.

When the program is compiled, if two functions with the same name are found and one of them is a weak function, the weak function will be ignored and the normal function will be used for compilation; if only one weak function is found, then the weak function will still be used to participate in the compilation.

When the upper layer uses it, just define another function which is the same, without specifying the weak function, and then add some user code to the function.

Interrupt site save and resume

No interrupt save and resume are found in the interrupt processing, but the function is normal for the following reasons:

_attribute_ ((interrupt ("machine"), aligned(4)));

There are interrupt declarations in attribute, and the compiler sees that it will insert code that modifies the protection registers.

Priority in external interrupt

When multiple interrupt sources initiate requests to the processor at the same time, the concept of interrupt priority exists when these interrupt sources need to be arbitrated and which interrupt sources are prioritized. When interrupt priority is not enabled, a new interrupt will not interrupt the interrupt being processed and will wait until the interrupt service function is completed before a new interrupt request can be responded accordingly. The default interrupt preemption function is not turned on, and if you need to use the interrupt preemption function, you need the following three steps:

a) Set plic_set_threshold(). Only interrupts with priority> threshold can be generated, threshold defaults to 0 and priority defaults to 1.

b) plic_preempt_feature_en(); //enable interrupt preemption function

c) plic_set_priority(); //set the interrupt priority

Note:

- The SoC has 4 interrupt priority 0-3. The interrupt source with no setting of interrupt priority, the default priority is 1, the larger the number the higher the priority. Setting to 0 priority will not generate interrupts (threshold default 0, do not meet the condition: priority> threshold). The high priority interrupt source can interrupt the interrupt source with lower priority, can not interrupt the interrupt with the same level priority.

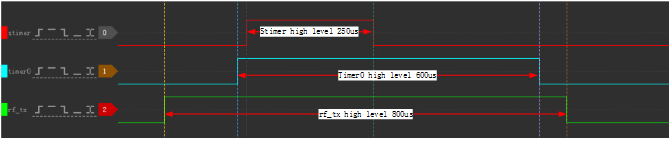

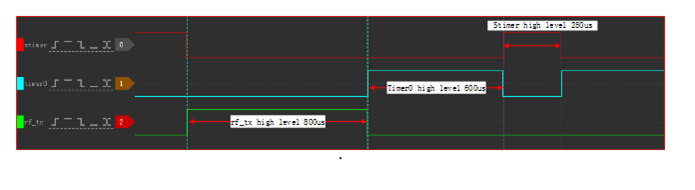

There are 3 interrupts configured in the demo, stimer interrupt, timer0 interrupt and rf_tx interrupt.

a) Enable interrupt

core_interrupt_enable();

b) Enable interrupt preemption, set priority, default threshold is 0

plic_preempt_feature_en(); //enable interrupt preemption

plic_set_priority(IRQ1_SYSTIMER,IRQ_PRI_LEV3); //set the stimer priority

plic_set_priority(IRQ4_TIMER0, IRQ_PRI_LEV2); //set timer0 priority

plic_set_priority(IRQ15_ZB_RT, IRQ_PRI_LEV1); //set rf priority

Before and after the delay of the interrupt handler function, the observation IO is set to pull up before the delay and pull down after the delay. In the demo, the stimer is delayed for 250us, the timer0 is delayed for 600us, and the rf_tx is delayed for 800us.

_attribute_ram_code_sec_noinline_ void irq_handler(void)

{ ...

gpio_set_high_level(LED3);

delay_us();

gpio_set_low_level(LED3);

}

Results observation

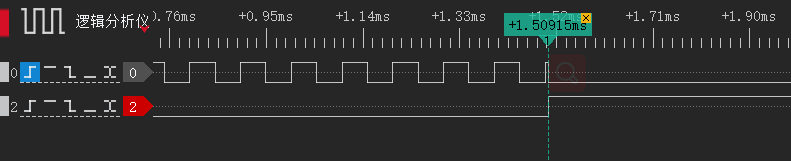

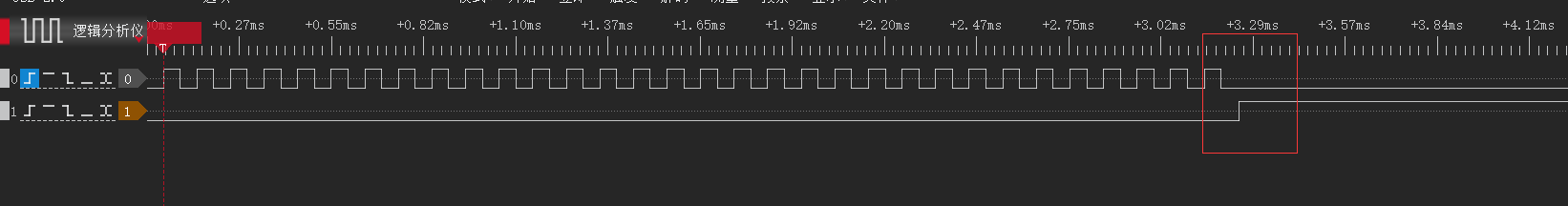

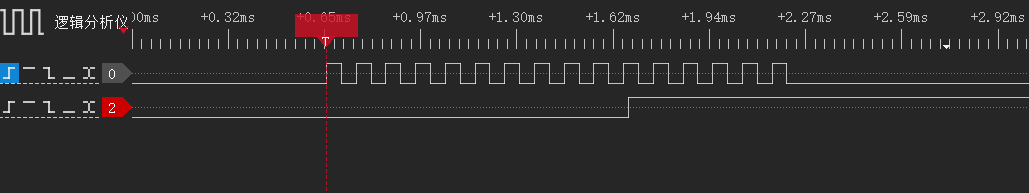

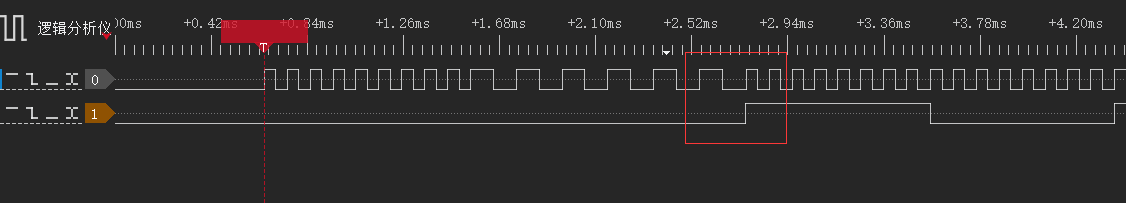

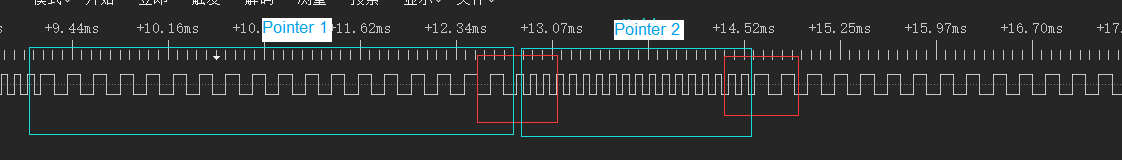

In the following figure, the interrupt nesting is enabled, rf_tx is interrupted by the high priority timer0, and so forth, Time0 interrupt handler function is interrupted by the higher priority stimer.

In the figure below, the interrupt nesting is not enabled, and the default priority of all three interrupt sources is 1. After the previous interrupt handler function is executed, the next interrupt handler function is processed without interrupts.

GPIO

The SoC's GPIO driver implements the configuration of GPIO inputs and outputs, pull-ups and pull-downs, interrupts, and other functions.

Interrupt

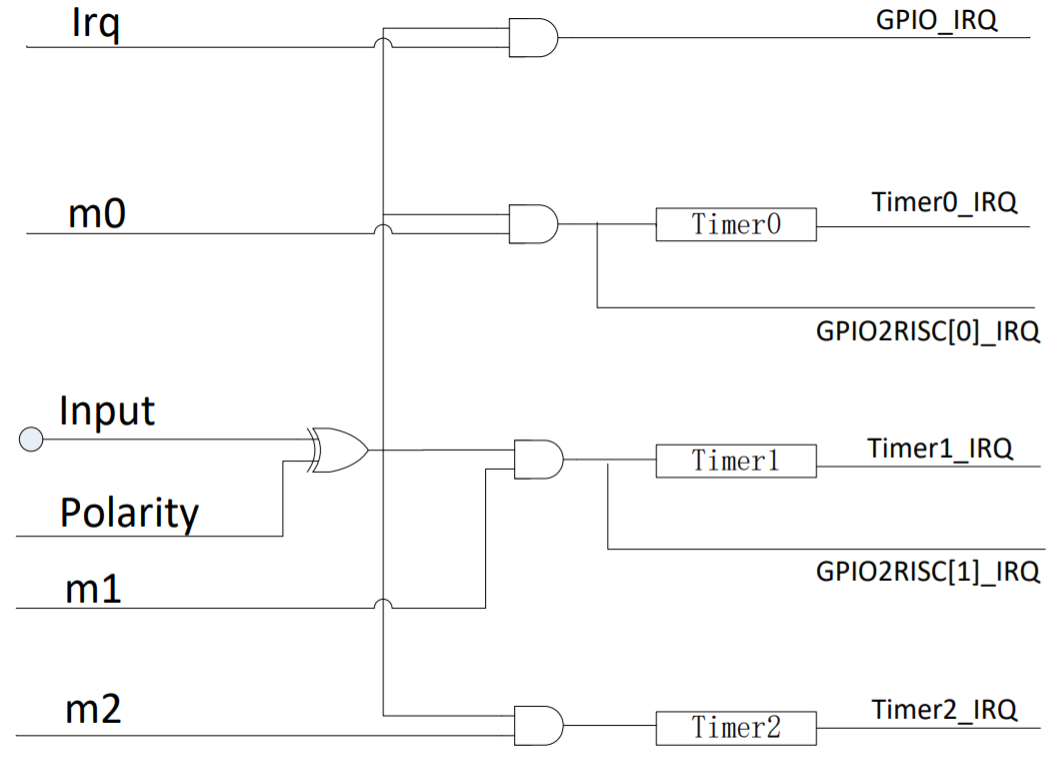

GPIO can be configured to generate interrupts. The interrupt hardware structure is shown in the figure below. Each GPIO can be configured to generate three types of interrupts, GPIO_IRQ, GPIO2RISC0_IRQ, and GPIO2RISC1_IRQ. GPIO_IRQ is the most basic GPIO interrupt, GPIO2RISC0_IRQ and GPIO2RISC1_IRQ can generate count or control signals in Timer (timer peripheral) applications, in addition to the GPIO_IRQ functions.

Mechanism description

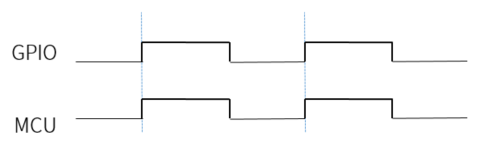

As shown in the figure below, the GPIO is set to trigger at rising edge. The mechanism of MCU is that the level signal of GPIO is used as the signal to generate interrupt and trigger the interrupt at rising edge.

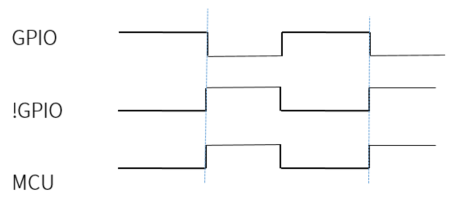

As shown in the figure below, the GPIO is set to trigger at falling edge. The mechanism of MCU is to invert the level signal of GPIO and then use the inverted signal as the signal for interrupt generation, and trigger the interrupt at rising edge.

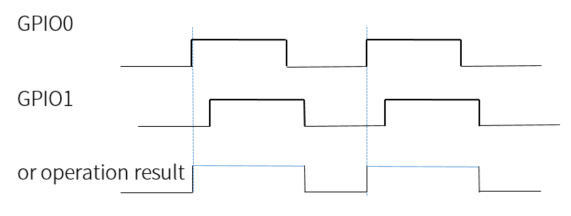

As shown in the figure below, if two GPIOs are set as one kind of interrupt, trigger at rising edge, the mechanism of MCU is that the level signal of two GPIOs will be or operation, and then use the obtained signal as the condition to generate interrupt, trigger the interrupt at rising edge. In this figure, only GPIO0 triggers the interrupt.

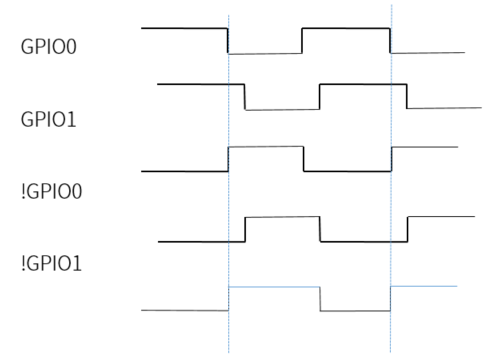

As shown in the figure below, if two GPIOs are set as one kind of interrupt, trigger at falling edge, the mechanism of MCU is to invert the level signals of two GPIOs respectively, and then make or operation for the inverted signal, and use the obtained signal as the condition to generate interrupt, which also triggers interrupt at rising edge. That is, finally MCU uses the final signal to trigger the interrupt at rising edge. In the figure, only GPIO0 triggers the interrupt.

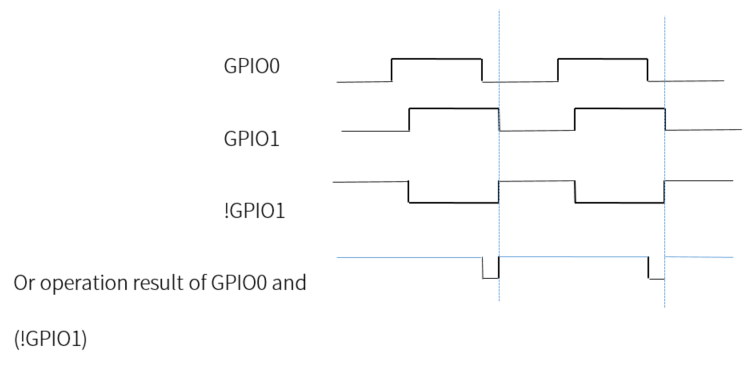

As shown in the figure below, if GPIO0 is set to trigger at rising edge and GPIO1 is set to trigger at falling edge, the mechanism of MCU is to invert the level signal of GPIO1, then make or operation for GPIO0 and (!GPIO1), and use the obtained signal as the condition to generate interrupt, which also trigger interrupt at rising edge. That is, finally MCU is using the final signal to trigger the interrupt at rising edge. In the figure, only GPIO1 triggers the interrupt.

Conclusion

Two or more GPIOs set as one kind of interrupt, depending on the timing of input GPIO, triggering interrupts is uncertain and not recommended. However, the mechanisms of different GPIO interrupts are independent of each other. If one GPIO is set to one kind of interrupt, the interrupts of both GPIOs can be triggered.

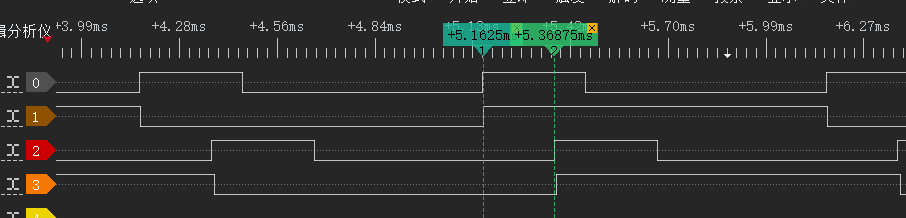

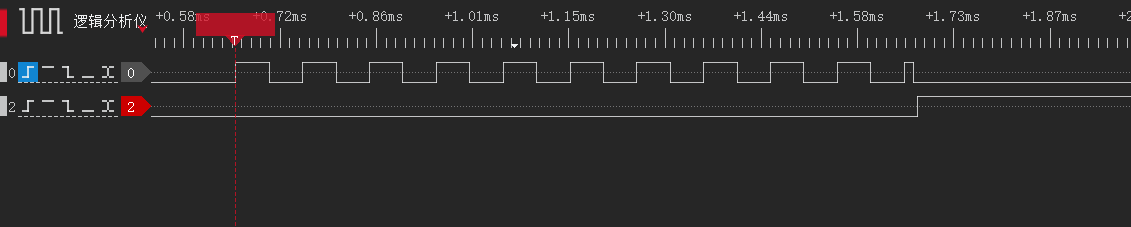

For example, GPIO0 is set to GPIO_IRQ interrupt and GPIO1 is set to GPIO_IRQ_RSIC0 interrupt, both configured to be triggered at rising edge. In the figure below, signals 0 and 1 are the input timing of GPIO0 and the toggle signal set within the interrupt handler function to observe the GPIO0 interrupt, and signals 2 and 3 are the input timing of GPIO1 and the toggle signal set within the interrupt handler function to observe the GPIO1 interrupt, respectively. In this figure, both GPIO1 and GPIO2 trigger the interrupt.

Note:

- Since there are only three GPIO interrupts, GPIO_IRQ, GPIO_IRQ_RSIC0, and GPIO_IRQ_RSIC1, up to three GPIO interrupts can be set at the same time.

Attentions

If setting the trigger type as high or trigger at rising edge, pull-down resistor should be set; if setting the trigger type as low or trigger at falling edge, pull-up resistor should be set.

Two other issues that do not require concern to the application layer are also briefly explained here (they are addressed in the driver interface).

When setting trigger at falling edge, you need to clear the interrupt bit after setting the polarity of GPIO, and then enable mask. (Otherwise, when setting GPIO to trigger at falling edge, a non-falling edge caused interrupt trigger is generated at the moment of enabling GPIO interrupt.) This part has been handled in the corresponding interrupt enable function of GPIO, and does not require the application layer to care.

GPIO multiplexing function switching notes:

(1) It starts with GPIO function, so you need to configure the required function MUX first, and then disable the GPIO function at the end.

(2) It starts with IO function, and needs to change to GPIO output. First set the corresponding IO output value and OEN set correctly, and enable GPIO function at the end.

(3) It starts with IO function, and needs to be changed to GPIO input.

Need pull up this IO:

Case 1 (digital pull-up): set output to 1 and OEN to 1;

Case 2 (analog pull-up): set pullup to 1.

No need to pull up:

Case 1 (digital pull-up): set output to 0 and OEN to 1;

Case 2 (analog pull-up): set pullup to 0.

Finally enable the GPIO function.

Clock

Brief description

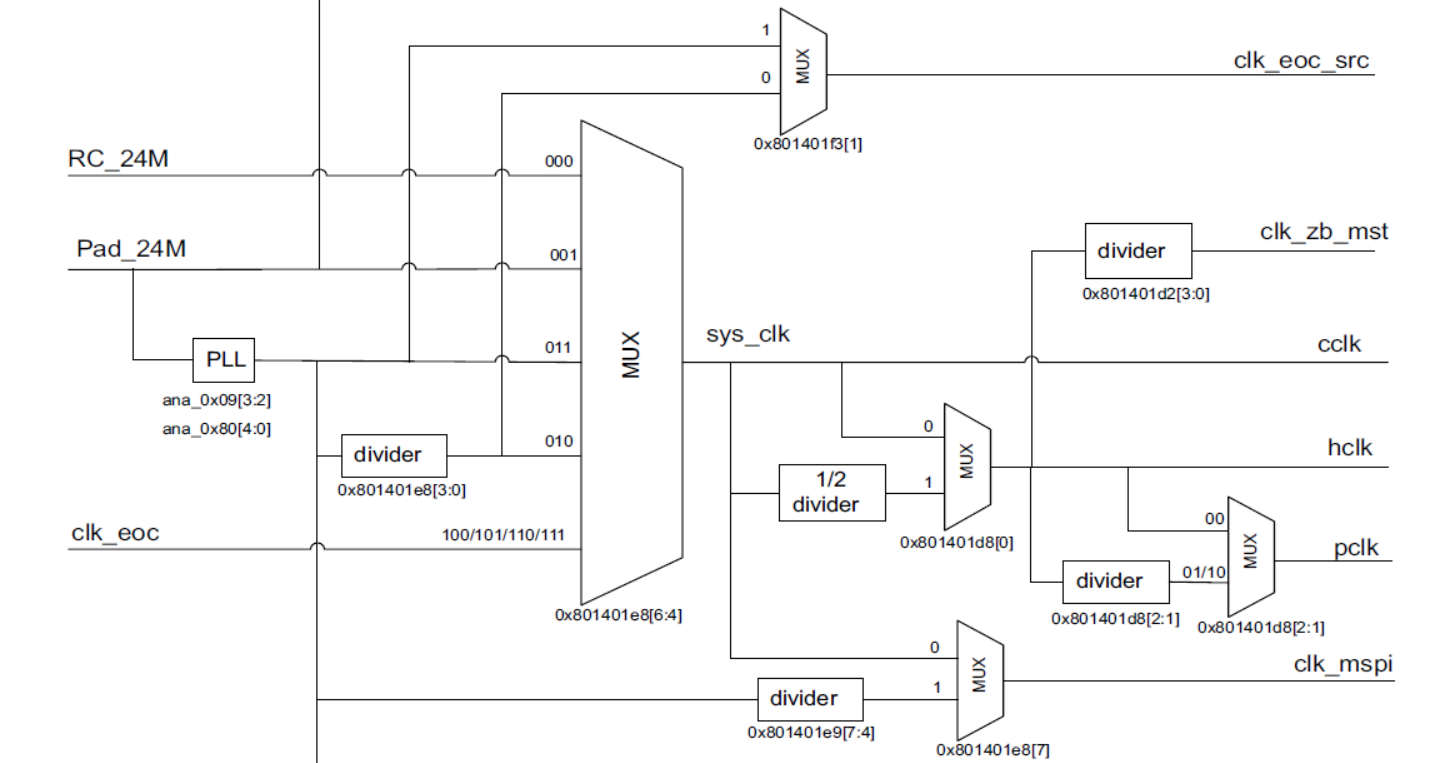

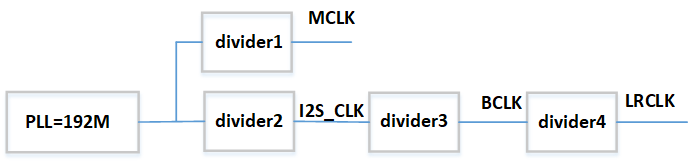

The clock of Risc-V Platform SoC is relatively complex, the following figure shows the clock tree for some of the clocks (the complete clock tree structure is in the datasheet). Here are a few of some important clocks, pll_clk/cclk/hclk/pclk/mspi_clk.

pll_clk: it is PLL in the figure, which is the source of many module clock sources, many clocks including sys_clk generally use frequency divided from PLL.

cclk: it is CPU clk, the speed of the program running is determined by this clock, and it is also the only clock source of hclk and pclk.

hclk: hclk is used by all modules hooked to the AHB bus.

pclk: pclk is used by all modules hooked to the APB bus.

mspi_clk: mspi connects to flash and performs flash-related operations, including fetching commands, reading and writing flash, and so on, all of which are controlled by this clock.

clock_init

The Driver provides the clock_init interface to configure the 5 clocks above.

Note:

- This function sets several clocks in addition to the parameters, and will also set the USB clock. The USB clock is using fixed 48M clock.

The maximum clocks currently supported are shown in the following table:

| clk | cclk | hclk | pclk | mspi |

|---|---|---|---|---|

| fre_max | 96M | 48M | 24M | External flash: 48M; internal flash: 64M |

PLL_CLK

Many clocks can be used, but if there is no special demand, 192M needs to be used uniformly.

Note:

- USB uses a fixed 48M clock, when configuring PLL_CLK, you need to pay attention to the fact that if the clock cannot be divided to get 48M, it may cause the USB not to work normally.

- In addition, some frequencies in the Audio driver are set in accordance with192M, modifying the PLL_CLOCK will lead to Audio errors.

CCLK

There are four optional clock sources for cclk, namely RC_24M, PAD_24M, PAD_PLL, and PAD_PLL_DIV, where PAD_PLL_DIV has an optional dividing frequency ratio of 2-15.

HCLK

The hclk is frequency divided from cclk, and can be 1 and 2 frequency division.

PCLK

The pclk is frequency divided from the hclk and can be 1, 2, or 4 frequency division.

Note:

- When hclk = 1/2 cclk, pclk can not be set to 4 frequency divisions, this is related to the hardware, which is processed in the interface. If set so, the program will stop and will not be executed for the next.

- In addition: in the case of using REBOOT or PM, if hclk selects 2 frequency divisions, there is a probability of causing a crash.

MSPI_CLK

The mspi clock has two optional clock sources, one is equal to cclk and the other is obtained by frequency devision from the PLL_clock.

AES

It supports hardware AES128 encryption, all buffer data used in the interface are using the small endian mode.

Note:

- This is because there is a restriction on the address where the data used in AES calculations can be stored: it must be in the address space of base_address+64K.

- It is currently handled in the driver as follows: Define the base_address as 0xc0000000 (that is the starting address of IRAM) in the first 64K of the IRAM range aes_data segment (which can be seen in the link file), and the data that needs to be processed during AES calculation are put into the aes_data segment for processing.

- If you do not change the location of the aes_data segment in the link file, you can use it directly without concerning the above process.

- If it does not meet the demand, you can also adjust it by yourself according to the demand. The driver provides aes_set_em_base_addr interface to modify the base_address.

- In addition, this address is shared with BT, and modifying it also requires ensuring that the data used by BT is also in this address space.

EMI

EMI samples are used with "EMI_Tool" and "Non_Signaling_Test_Tool" tools. This document mainly introduces related functions and considerations in the EMI test samples.

Protocol

Please refer to the Telink SoC EMI Test User Guide for the communication protocol.

Program description

EMI testing in Eagle supports carrieronly mode, continue mode, burst mode, and packet-receiving mode.

The supported wireless communication methods include Ble1M, Ble2M, Ble125K, Ble500K, and Zigbee250K.

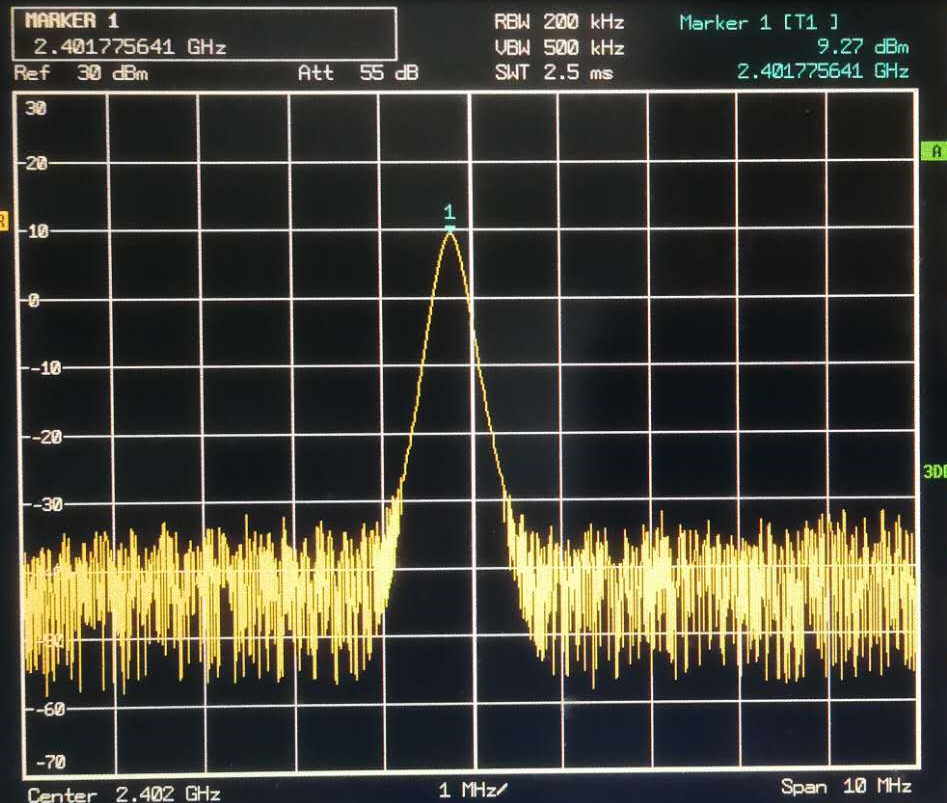

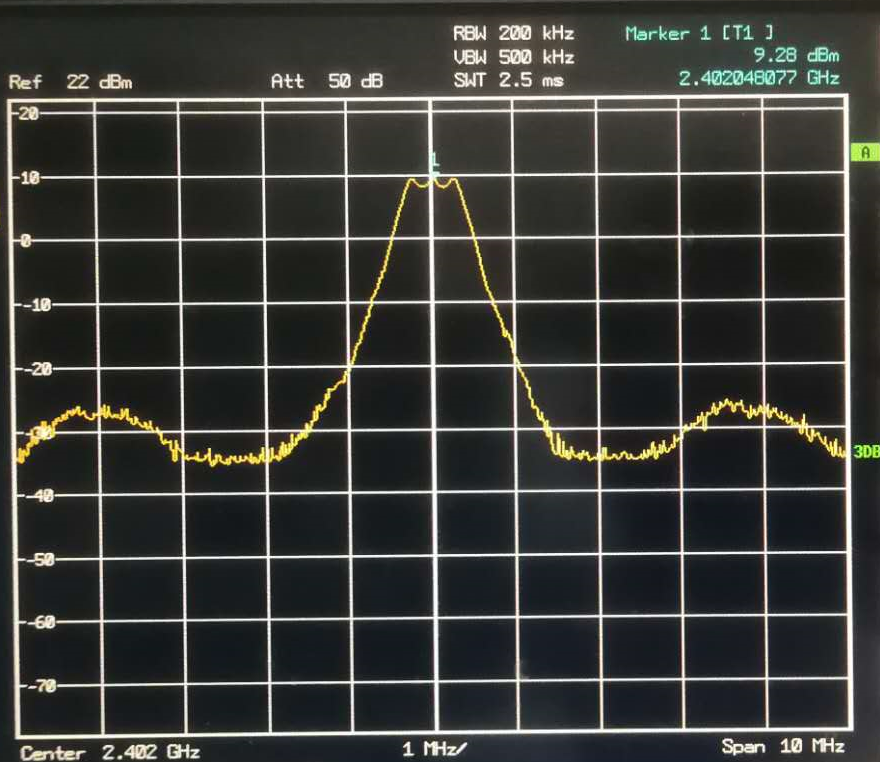

CarrierOnly mode

Function: The CarrierOnly mode is used to generate a single-pass signal. In this mode, you can set the channel, power value and the communication mode (rf mode) for the single-pass signal.

Example:

Test tool: select EMI_Tool

Wireless communication mode setting: Ble1M/Ble2M/Ble125K/Ble500K/Zigbee250K

Power setting: XXdB

Channel setting: 2402~2480MHz

Continue mode

Function: The continue mode is used to generate a continuous signal, in which the channel, power value as well as the communication mode (rf mode) can be set.

The continue mode sending packet (Payload) data includes Prbs9, 0x0f, and 0x55, and can set frequency hop.

Example:

Test tool: select EMI_Tool

Wireless communication mode setting: Ble1M/Ble2M/Ble125K/Ble500K/Zigbee250K

Power setting: XXdB

Channel setting: 2402~2480MHz

Note:

- Currently EMI_Tool only supports sending prbs9 packets in continue mode.

Burst mode

Function: The burst mode allows you to set the channel, power value and the communication mode (rf mode) for the Burst signal.

The burst mode sending packet (Payload) data includes Prbs9, 0x0f, and 0x55.

Example:

Test tool: select Non_Signaling_Test_Tool

Wireless communication mode setting: Ble1M/Ble2M/Ble125K/Ble500K/Zigbee250K

Power setting: XXdB

Channel setting: 2402~2480MHz

Note:

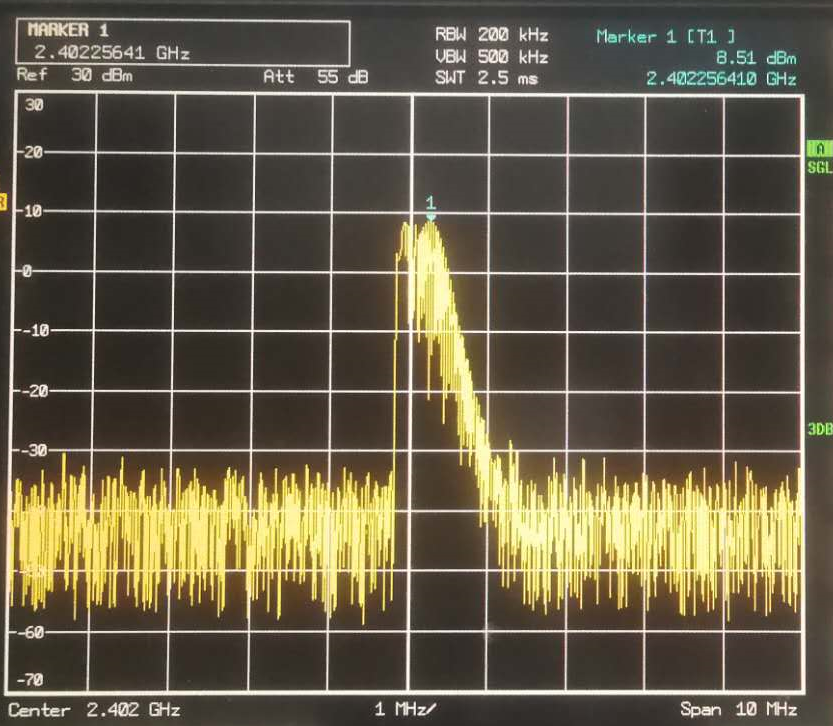

- Due to the discontinuous signal in Burst mode, the Single Sweep and MaxHold settings of the spectrum analyzer can be used to capture the signal.

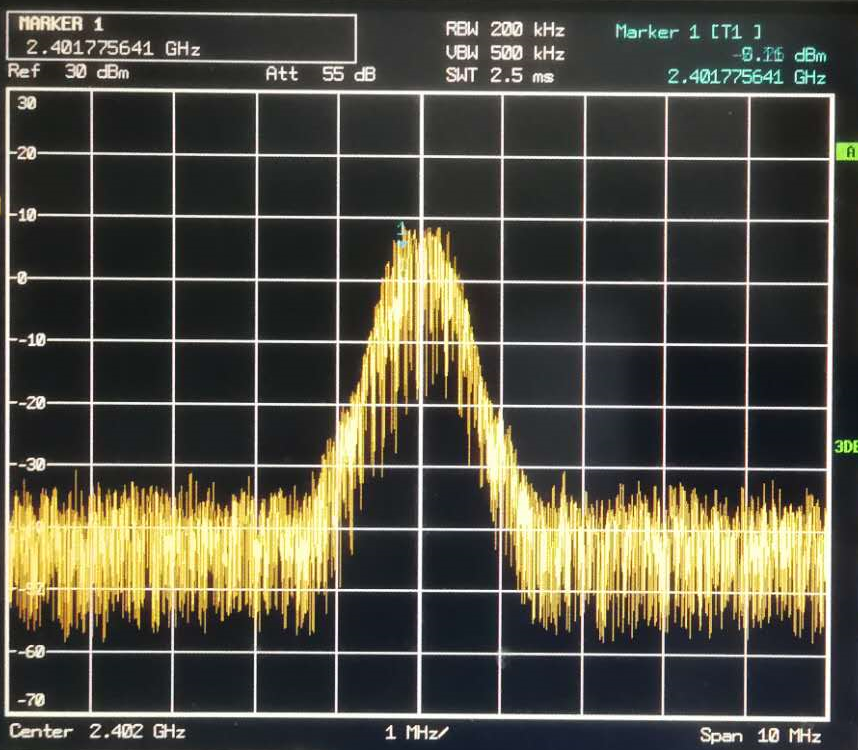

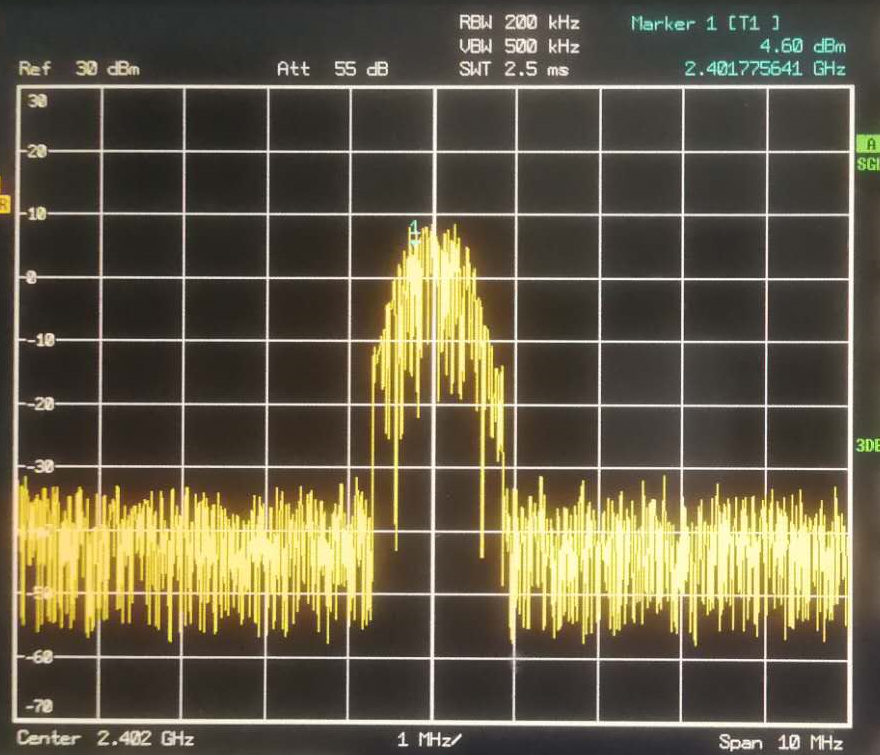

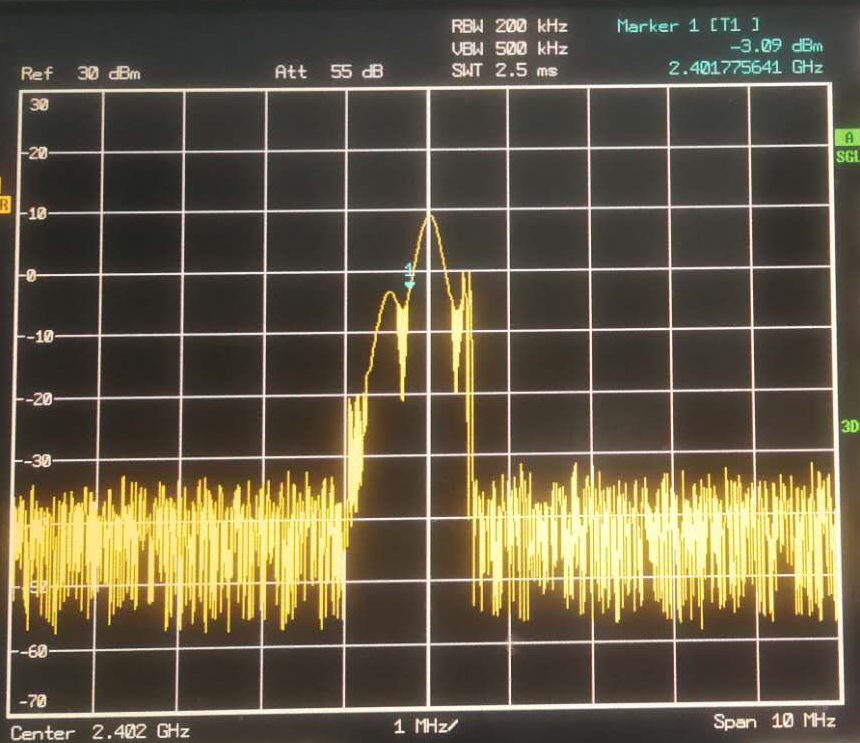

The first three pictures below are the results of the Single Sweep setting, and the fourth picture is the result of the MaxHold setting.

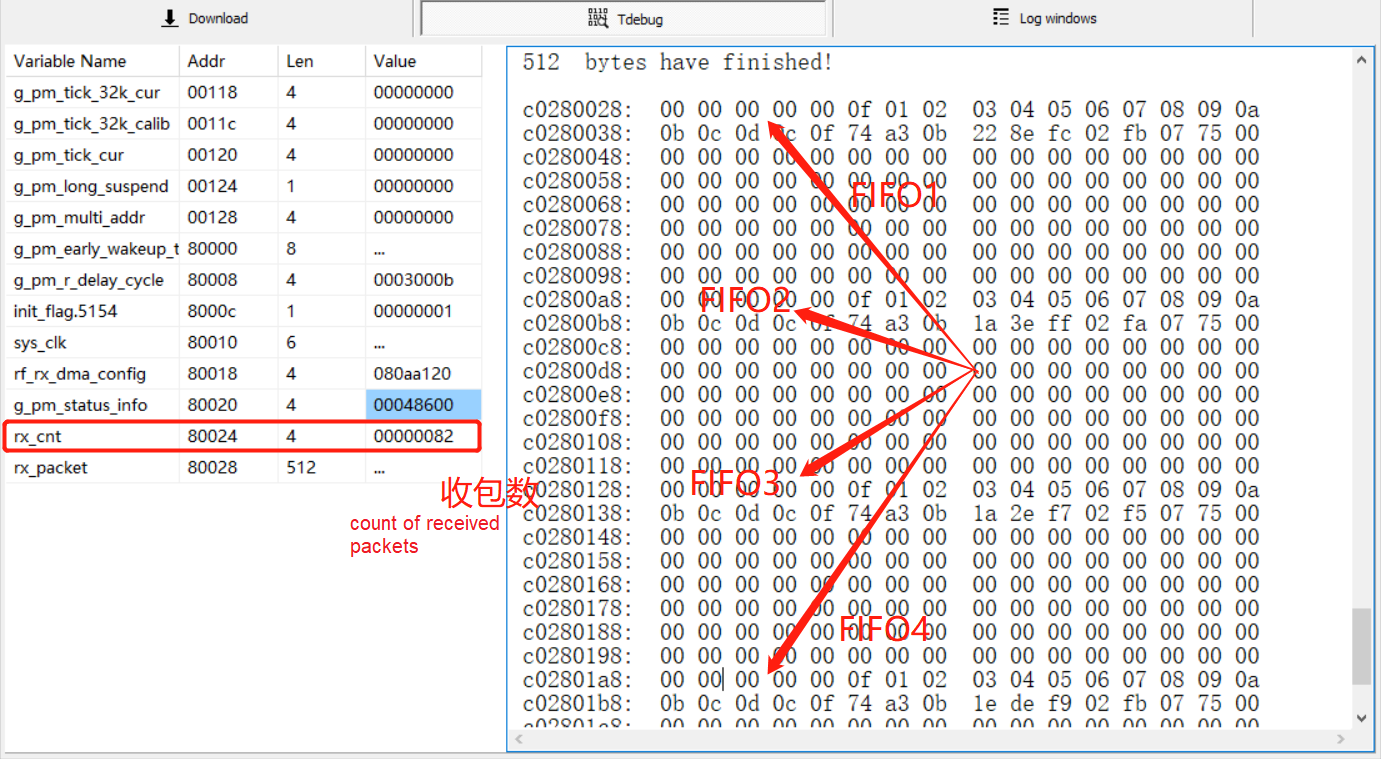

RX Mode

Function: In the packet-receiving mode, communication mode can be set to receive packets, specifically with the non-signaling test tool "Non_Signaling_Test_Tool" to obtain the number of packets received and RSSI.

Example:

Test tool: select Non_Signaling_Test_Tool

Wireless communication mode setting: Ble1M/Ble2M/Ble125K/Ble500K/Zigbee250K

Channel setting: 2402~2480MHz

Timer

This SoC supports 2 timers: Timer0 and Timer1.

The following four modes are supported: System Clock Mode, GPIO Trigger Mode, GPIO Pulse Width Mode, and Tick Mode.

There is also a watchdog timer, configured as "watchdog" to monitor system operation and reboot if there is an exception.

Function description

When using Timer0, Timer1 timers, you need to specify which mode to use by setting the timer_set_mode function interface:

void timer_set_mode(timer_type_e type, timer_mode_e mode,unsigned int init_tick, unsigned int cap_tick).

When using GPIO Trigger Mode and GPIO Pulse Width Mode of Timer0 and Timer1, the clock source of Timer is provided by GPIO, which needs to be set through the following interface. You can select GPIO and polarity, and the corresponding GPIO interrupt mask will also be set in this interface, so that the timer interrupt can be generated normally.

void timer_gpio_init(timer_type_e type, gpio_pin_e pin, gpio_pol_e pol ).

System Clock Mode

| Clock Source | Function | Mechanism Description |

|---|---|---|

| pclk | Timed interrupt generation | After setting to this mode, when a rising edge of pclk is detected, count register of the timer will add 1 until reaching the capture value, generating an interrupt, and at the same time, initial_tick will be automatically loaded, and recounted, and when reaching capture value, the interrupt will be entered again, timer enable is not turned off, so that this operation will be cyclic all the time. |

Setup steps (as the following code):

timer_set_mode(TIMER0, TIMER_MODE_SYSCLK, 0, 50*sys_clk.pclk*1000);

timer_start(TIMER0);

GPIO Trigger Mode

| Clock Source | Function | Mechanism Description |

|---|---|---|

| Provided by GPIO | Specific number of GPIO rising/falling edge triggers interrupts | After setting to this mode, the timer will count plus 1 for every rising/falling edge of GPIO. When the timer count value reaches the specified set number, an interrupt will be performed, the timer will be cleared to start counting again. The timer enable interrupt is not turned off, so that the operation will be cyclic all the time. |

Setup steps (as the following code):

timer_gpio_init(TIMER0, SW1,POL_RISING);

timer_set_mode(TIMER0, TIMER_MODE_GPIO_TRIGGER,0,TIMER_MODE_GPIO_TRIGGER_TICK);

timer_start(TIMER0);

GPIO Pulse Width Mode

| Clock Source | Function | Mechanism Description |

|---|---|---|

| pclk | Capture pulse width | After setting to this mode, if the set GPIO detects a rising/falling edge, it will trigger the timer timing. For every pclk, the timer will count plus 1. When the GPIO level invert is detected, it will enter the interrupt, the timer count stops, at this time the current tick count value can be read to calculate the width of the GPIO pulse. This interrupt is triggered once, will not operate in automatic loop. |

Setup steps (as the following code):

timer_gpio_init(TIMER0, SW1, POL_FALLING);

timer_set_mode(TIMER0, TIMER_MODE_GPIO_WIDTH,0,0);

timer_start(TIMER0);

Example: If the polarity is set to POL_FALLING, the timing is triggered at the falling edge and the interrupt is generated at the rising edge.

Tick Mode

| Clock Source | Function | Mechanism Description |

|---|---|---|

| pclk | Can be used as a time indicator, this mode does not generate interrupt | After setting to this mode, the timer will count plus 1 for every rising/falling edge of GPIO. When the timer count value reaches the specified set number, an interrupt will be performed, the timer will be cleared to start counting again. If the initial count value of the timer is not set to 0 at the specified time, then the timer will keep adding 1 until the timer count overflows, automatically setting the initial count value of the timer to 0 and starting the timer again, and the timer will keep cycling through the timer like a clock. |

Setup steps (as the following code):

timer_set_mode(TIMER0, TIMER_MODE_TICK,0,0);

timer_start(TIMER0);

Watchdog Mode

| Clock Source | Function | Mechanism Description |

|---|---|---|

| pclk | Reset if you do not "feed the dog" within the set time After setting to this mode, the watchdog starts timing. If the dog is not fed within the specified time, the program will reset. The dog feeding function is: wd_clear_cnt, this function will clear the timing and restart the timing. If the watchdog is not used, you need to turn off the watchdog to avoid the program reset. |

Setup steps (as the following code):

wd_set_interval_ms(1000,sys_clk.pclk*1000);

wd_start();

Demo description

Choose which mode to use using the macro TIMER_MODE in Timer_Demo/app_config.h.

#define TIMER_SYS_CLOCK_MODE 1

#define TIMER_GPIO_TRIGGER_MODE 2

#define TIMER_GPIO_WIDTH_MODE 3

GPIO System Clock Mode

Demo setting:

Timer0, set to system clock mode, set initial_tick=0, capture value=50ms, enable timer0. Interrupt will be reversed using LED2.

Execution result:

LED2 will be reversed every 50ms, resulting in the following:

Channel 1 (LED2): is an interrupt marker GPIO, about 50ms, reversing once.

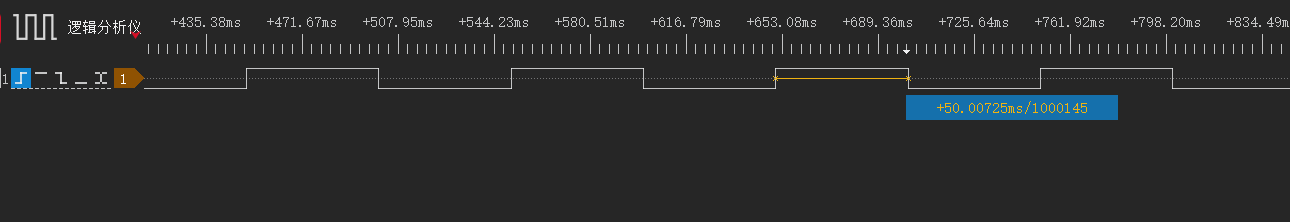

GPIO Trigger Mode

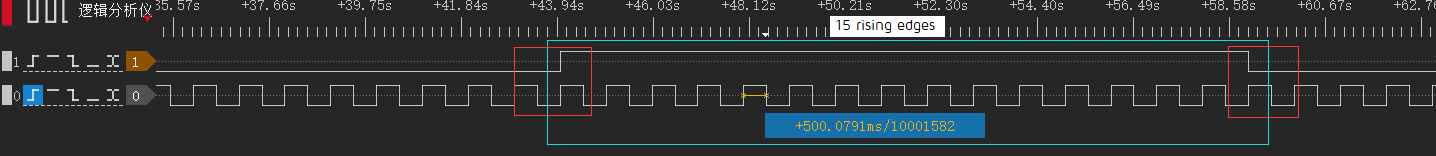

Demo setting:

Timer0, set to GPIO trigger mode, initialize GPIO, configure SW1 as timer0s clock source, trigger at rising edge, set initial_tick=0, value=0xf, enable timer0. Interconnect GPIO_PA2 and SW1 pins, GPIO_PA2 generates a rising edge every 500ms, when reaching the capture value, it enters an interrupt. The interrupt will be reversed using GPIO_PB5.

Execution result:

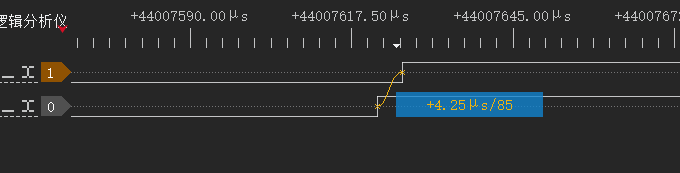

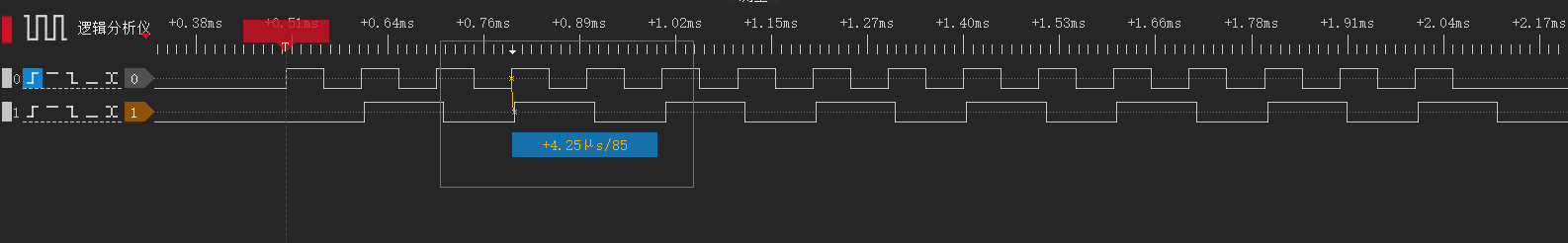

For every 15 rising edges generated by GPIO_PA2, LED2 reverses once, resulting in the following:

Channel 1 (LED2): is the interrupt marker GPIO, for every 15 rising edges generated by GPIO_PA2, LED2 generates a reverse.

Channel 0 (GPIO_PA2): is the trigger signal pin GPIO_PA2.

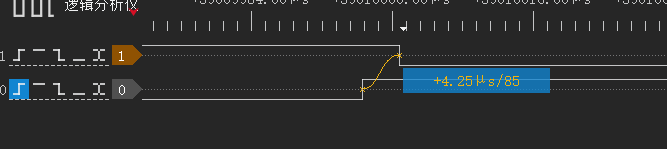

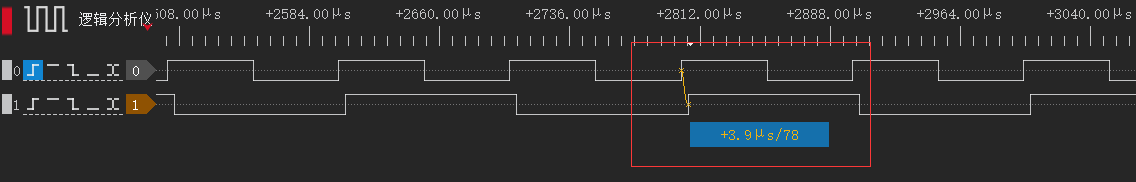

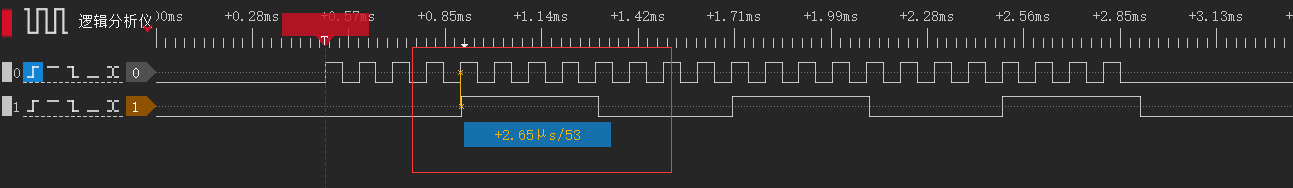

The following is detailed description of the red box:

As you can see from the red box 1 and 2, after the 15th rising edge of the previous interrupt, the delay is about 4.25us, it will enter the current interrupt, and LED2 will be reversed. And after the current LED2 lasts for 15 rising edges, the delay is about 4.25us and it will enter the next interrupt.

GPIO Pulse Width Mode

Demo setting:

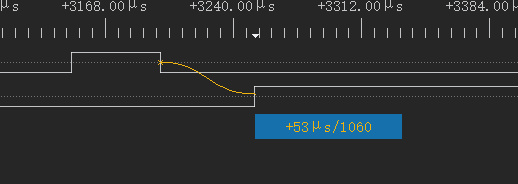

Timer0, set to GPIO pulse width mode, initialize GPIO, configure SW1 as trigger source for timer0, trigger at falling edge, set initial_tick=0, capture value=0, enable timer0. Interconnect GPIO_PA2 and SW1 pins, GPIO_PA2 generates a falling edge, trigger timer timing, delay 250ms, GPIO_PA2 generate a rising edge, it enters an interrupt. The interrupt will be reversed using LED2.

Execution result:

When GPIO_PA2 generates a rising edge, LED2 reverses and the result is as follows:

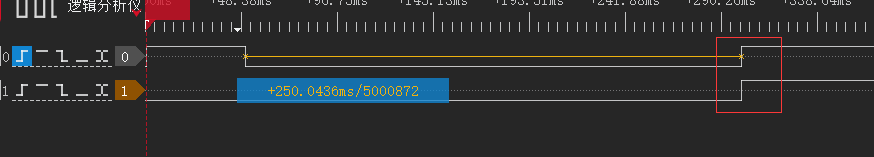

Channel 0 (GPIO_PB4): is the waveform of trigger source GPIO_PA2.

Channel 1 (LED2): is an interrupt marker GPIO, detects that GPIO_PA2 generates a rising edge, an interrupt occurs, and LED2 generates a reverse.

The time delay for generating interrupts is 4.75us, and the CPU entering the interrupt needs a certain amount of software and hardware processing time.

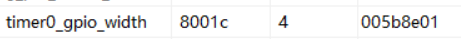

Reading the timing register of the timer results in the following:

For 0x005b8e01 hexadecimal conversion to decimal, the result is 6000129, using the system clock, the frequency is 24M, every 1/24M seconds count once, 6000129 * (1/24M) calculated to be about 250ms.

Tick Mode

Demo setting:

Timer0, set to tick mode, set initial_tick=0, capture value=0, enable timer0. Every 500ms, manually set the timer timing to start from the beginning and LED2 reverses once.

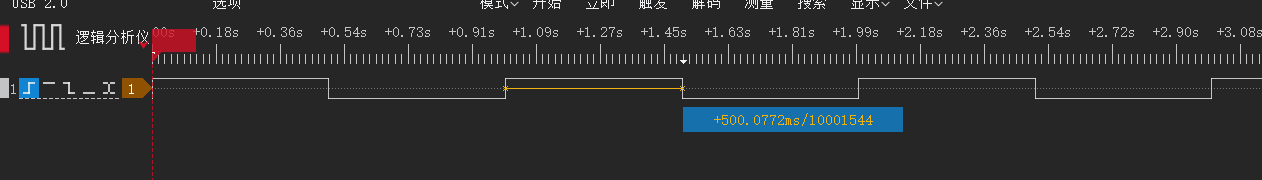

Execution result:

LED2 will be reversed every 500ms, resulting in the following:

Channel 1 (LED2): is tick mode marker GPIO, which is reversed once every 500ms or so.

Watchdog Mode

(1) Dog-feeding test

Demo setting:

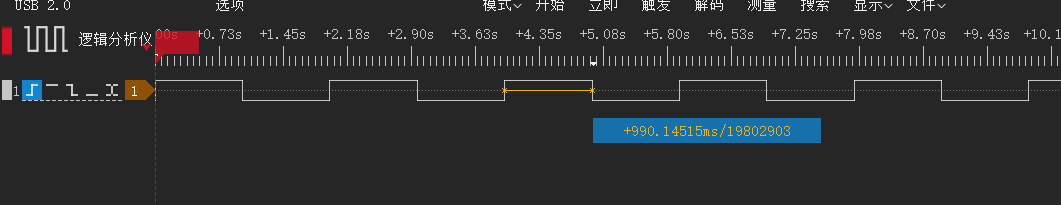

Set the watchdog time, reg_wt_target=1000ms. Every 990ms, feed the dog and LED2 reverses once.

Execution result:

LED2 will be reversed every 990ms, resulting in the following:

Channel 1 (LED2): is the dog-feeding test marker GPIO, which is reversed every 990ms or so.

(2) No dog-feeding test

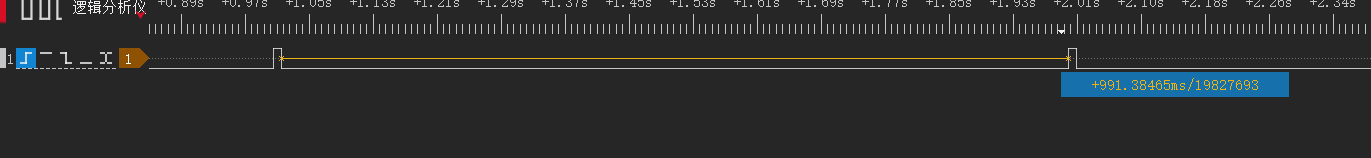

If the dog is not fed within the set watchdog time.

Demo setting:

delay_ms(990);

//wd_clear_cnt(); //cancel the dog feeding operation

gpio_toggle(LED2);

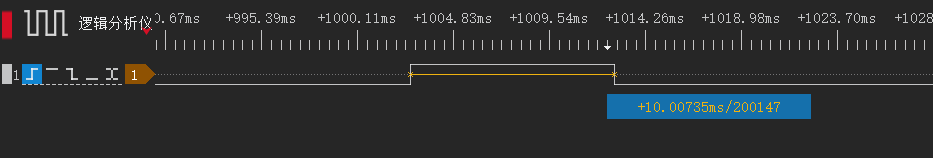

Execution result:

LED2 will periodically output a waveform with a low level of 991.3847ms and a high level of 10.0074ms, resulting in the following:

Channel 1 (LED2): is no dog-feeding test marker GPIO.

Result: The time set for watchdog is 1000ms, after 990ms delay, reverse LED2, as there is no dog feeding, LED2 high level state is maintained for 10ms, after reaching the time set for watchdog, the program resets and keeps repeating the above operation.

Analog

The analog driver is used to read and write analog registers, supporting the function test of single Byte/Hword/Word, data buffer, DMA channel read and write.

Attentions

When using DMA to read data from analog registers to buffer, the buffer size of the corresponding destination address must be a multiple of 4.

The reason: Each DMA sends 4 bytes to buffer. 4 bytes will be written to the destination address even if the configured read length is less than 4.

For example: if you define an array buffer of size 5 bytes and configure the DMA to read 5 bytes from the analog register to buffer, the DMA actually transfers twice and 8 bytes in total to buffer, and the extra 3 bytes data will overflow from the array, and the overflowed data will overwrite other variables. At this time, if the array size is configured to 8 bytes, the extra 3 bytes data will be stored in the array and will not be overflowed, avoiding the potential risk.

Speed Test

Under the condition that cclk, pclk and hclk are set to 24MHz, each interface function is loaded into RAM and the time spent on reading and writing 4 bytes and 8 bytes in each mode is tested as follows:

| Mode | Time of writing 4 bytes | Time of reading 4 bytes |

|---|---|---|

| ALG_WORD_MODE | 6us | 12.9us |

| ALG_DMA_WORD_MODE | 8.4us | 10.2us |

| ALG_DMA_BUFF_MODE | 8.4us | 12.4us |

| ALG_BUFF_MODE | 10us | 12us |

| ALG_HWORD_MODE | 12.8us | 17.6us |

| ALG_DMA_ADDR_DATA_MODE | 13.1us | Not supported |

| ALG_BYTE_MODE | 22.6us | 26.8us |

| Mode | Time of writing 8 bytes | Time of reading 8 bytes |

|---|---|---|

| ALG_DMA_BUFF_MODE | 11.2us | 15.5us |

| ALG_BUFF_MODE | 12.8us | 16.6us |

| ALG_WORD_MODE | 15.8us | 19.3us |

| ALG_DMA_ADDR_DATA_MODE | 18.9us | Not supported |

| ALG_DMA_WORD_MODE | 23.5us | 20.1us |

| ALG_HWORD_MODE | 24.8us | 32.9us |

| ALG_BYTE_MODE | 44.1us | 53.9us |

Flash

The flash is a Non-Volatile memory that can retain data for a long time without current supply and has storage characteristics equivalent to a hard disk. The flash can erase and reprogram memory cells called blocks. The write operation of any flash device can only be performed in an empty or erased cell, so an erase must be performed before a write operation can be performed.

Read operation

Note:

- When the read address exceeds the maximum address of flash, the value can still be read, but the read address is calculated according to the valid address bits. (If the flash size is 1M bytes, the maximum address is 0xfffff, that is, the lower 20 bits is the valid address bit; if the value of 0x100000 address is read, the value of 0x0 address is read.)

Write operation

Note:

- You should erase before write. The latest flash_write_page function supports cross-page writing.

BQB

This section describes how to use the BQB to test Demo.

Function description

-

Supports 2-wire mode;

-

Supports BLE1M, BLE2M, BLE_LR_S2/S8;

-

Supports long packages (payload of 255);

-

Supports manual adjustment of frequency bias values by writing flash;

-

Supports manual adjustment of serial port configuration by writing flash.

Frequency bias value setting

The flash addresses of 0x7e000 (512K), 0xfe000 (1M), and 0x1fe000 (2M) are used to set the frequency bias value, and the setting is made effective by a reset after writing the frequency bias value. If the value is not written, (0xff) is the default frequency bias value.

Communication verification

After the serial port configuration is complete you can verify that the serial port is communicating properly by the following method:

Open the serial port tool on the PC and send "C0 00" in hexadecimal format to Eagle development board. If you can receive the response of "80 00" from the board, it means the communication is normal.

PWM

PWM introduction

The SoC has 6 PWM channels: PWM0~PWM5.

The relevant modes supported by PWM are described as follows:

Modes supported by PWM0:

- continuous mode

- counting mode

- IR mode

- IR FIFO mode

- IR DMA FIFO mode

Modes supported by PWM1~PWM5:

- continuous mode

Clock

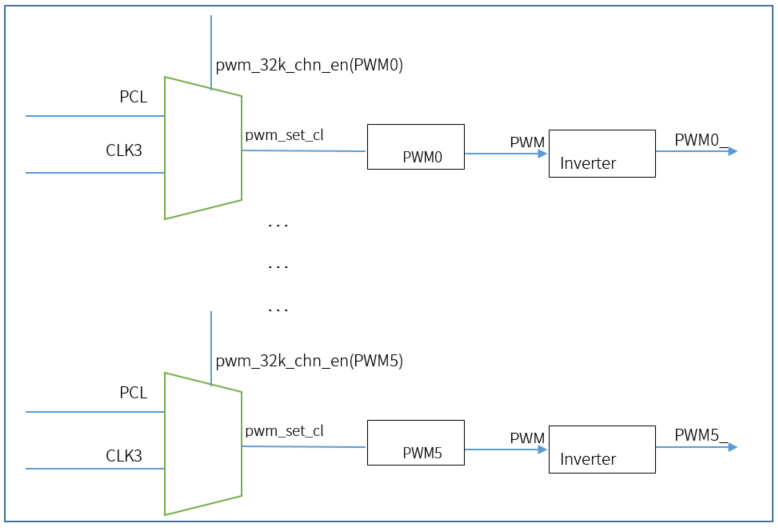

The PWM clock source is available in two ways, either pclk or 32K, as shown below:

pclk:

Function: The clock can be frequency divided and then the divided clock is used as the clock source for PWM.

Interface configuration: static inline void pwm_set_clk(unsigned char pwm_clk_div);

Where: pwm_clk_div = pclk_frequency /pwm_frequency -1; (pwm_clk_div: 0~255)

32K:

Function: The frequency division is not supported. It only supports continuous mode and counting mode. This configuration is mainly for the purpose of sending PWM waveforms even in suspend mode.

Interface configuration: static inline void pwm_32k_chn_en(pwm_clk_32k_en_chn_e pwm_32K_en_chn);

Note:

- All channels use pclk clock source by default. If you want to use 32K clock source, call pwm_32k_chn_en to enable the corresponding channel, the channel that is not enabled still uses pclk clock source.

- For 32K clock source, PWM design only considered when the suspend scenario, using interrupts in continuous mode and counting mode it will enter the interrupt a 32K clock cycle in advance, in this 32K clock cycle, it will exit the interrupt and enter the interrupt. When using 32K PWM, if you need interrupt, it is recommended using GPIO interrupt to achieve the interrupt.

- When using 32K clock source, if you need to update the duty cycle during operation, only calling the function to set the duty cycle will not take effect, you should set the duty cycle and then call the following function before it will take effect.

The specific function interface is as follows:

static inline void pwm_32k_chn_update_duty_cycle(void);

Duty cycle

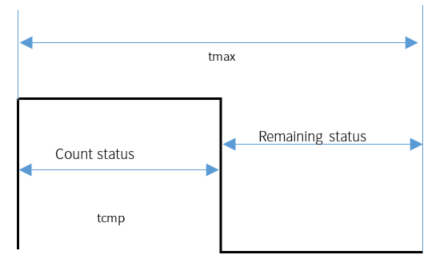

A signal frame of PWM consists of two parts, Count status (high level time) and Remaining status (low level time). And the specific waveform of a signal frame is as follows, where tmax is the cycle time.

The functions to set the signal frame period and duty cycle in the driver both use tcmp and tmax as parameters.

a) Generic function interface for setting duty cycle (all channels supported):

static inline void pwm_set_tcmp(pwm_id_e id, unsigned short tcmp);

static inline void pwm_set_tmax(pwm_id_e id, unsigned short tmax);

pwm_set_tcmp:

id: select which PWM channel;

tcmp: set the high level duration.

pwm_set_tmax:

id: select which PWM channel;

tmax: set period.

Note:

- The second parameter in the pwm_set_tmax function sets the period of PWM, the parameter type is short, the minimum value of tmax is 1 and cannot be 0. If tmax is 0, the pwm is in a non-working state, so the value of tmax is in the range of 1~65535.

- The second parameter in the pwm_set_tcmp function sets the duty cycle of PWM, and the parameter type is short. The minimum value of tcmp can be 0, when it is 0, the waveform of pwm is always low, and the maximum value can be tmax, when the waveform of pwm is always high, so the value range of tcmp is: 0~tmax.

b) When using the IR FIFO Mode and IR DMA FIFO Mode of PWM0, another function interface will be used:

static inline void pwm_set_pwm0_tcmp_and_tmax_shadow(unsigned short tmac_tick, unsigned short cmp_tick);

Note:

- In the pwm_set_pwm0_tcmp_and_tmax_shadow function, the parameter tmac_tick sets the cycle of pwm0, and the parameter cmp_tick sets the high level duration of pwm0. The value range of tmac_tick: 1 \~ 65536, and the value range of cmp_tick: 0 \~ cycle_ tick.

c) When using the counting mode and IR mode of PWM0, pwm0 needs to set the number of pulses output function, using the following function interface:

static inline void pwm_set_pwm0_pulse_num(unsigned short pulse_num);

pulse_num: the number of pulses.

d) When pwm0 writes cfg data to the fifo, the following function interface is used:

static inline void pwm_set_pwm0_ir_fifo_cfg_data(unsigned short pulse_num, unsigned char use_shadow, unsigned char carrier_en);

use_shadow:

1: Use the period and duty cycle set under the pwm_set_pwm0_tcmp_and_tmax_shadow function.

0: Use the period and duty cycle set under pwm_set_tmax, pwm_set_tcmp function.

carrier_en:

1: Output pulse according to the settings of pulse_num and use_shadow.

0: Output low level, duration is calculated according to parameters pulse_num and use_shadow.

Invert/polarity

(1) The waveform set by pwm_set_tcmp and pwm_set_tmax will output high level of Count status first and low level of Remaining status later by default.

(2) If PWM*_PIN is used, the output waveform is the same as the waveform set by pwm_set_tcmp and pwm_set_tmax.

(3) If PWM*_N_PIN is used, the output waveform is the opposite of PWM*_PIN waveform.

(4) If the PWM* channel invert function is enabled using pwm_invert_en, it will flip the PWM*_PIN waveform.

(5) If the PWM* channel invert function is enabled using pwm_n_invert_en, it will flip the PWM*_N_PIN waveform.

(6) If the polarity function of PWM* channels is enabled using pwm_set_polarity_en, all PWM_PINs will be output according to the following rule: Count status outputs low, Remaining status outputs high.

Function description

Continuous mode

This mode will keep sending signal at the set duty cycle, set stop if you want to stop, and stop immediately after setting. During sending, the duty cycle can be updated, and the duty cycle will take effect at the next frame.

Counting Mode

It will stop once sending a set number of signal frames. In this mode, if stop, it will stop immediately. In this mode, modifying the duty cycle during sending will not change the duty cycle.

IR Mode

It sends pulse groups continuously in IR mode, and the duty cycle can be changed in between and will take effect on the next pulse group. If you want to stop it immediately, you can stop it directly. The difference between IR mode and counting mode is that it sends one pulse group and then stops sending in counting mode, while it sends pulse groups continuously in IR mode.

If you want to stop IR mode and finish the current pulse group, you can switch to counting mode.

If you want to stop immediately, you can stop directly.

Note:

- If you want to stop IR mode and finish the current pulse group, you can switch to counting mode in the interrupt, but during the switching process, the pulse group in the current IR mode will be sent out before switching over.

IR FIFO mode

The long code pattern can be sent without the MCU intervention. The IR carrier frequency is obtained by dividing the system clock and can support common frequencies. The element "Fifo cfg data" is used as the base unit of the IR waveform, and the hardware will parse the cfg information to send the corresponding signal.

In the IR FIFO mode it takes out the cfg data in the FIFO in turn and sends the corresponding signal until the fifo is empty. In this mode, you can use stop, but it only stops the execution of the current cfg data and does not affect the execution of the cfg data after the fifo.

Note:

- In IR FIFO mode, as long as the fifo has data, it will keep sending out (auto send), no start signal is needed, also IR DMA FIFO mode does not need start signal, but in all other modes, pwm_start signal is needed.

- Every time the function pwm_set_pwm0_ir_fifo_cfg_data is called, the cnt of the FIFO is added by 1 (if the FIFO is full at this time, it waits until the FIFO is not full and then writes), and the hardware takes one out from the FIFO, the cnt in the FIFO is subtracted by 1. The depth of the FIFO is 8 bytes. After the data is taken out from the FIFO, the send signal action is executed, and only after the current signal is executed, the next one will be taken out from the FIFO.

IR DMA FIFO mode

The IR DMA FIFO mode is similar to IR FIFO mode, except that the configuration is not written directly by the MCU in the FIFO, but is written to the FIFO via DMA.

Note:

- Inside the interrupt you need to update the DMA part of the configuration: update of the source address, DMA triggering, and so on.

- In this mode, unlike the IR FIFO, the interrupt is not triggered when the number of cfg data in the FIFO is empty, but only when all the configuration pwm signal frames in the fifo are executed.

Interrupts

The interrupt settings supported by PWM are described as follows (hardware does not automatically clear the interrupt flag bit, it needs to be cleared manually by software).

Interrupts supported by PWM0:

a) FLD_PWM0_FRAME_DONE_IRQ: Each signal frame is completed and an interrupt is generated.

b) FLD_PWM0_PNUM_IRQ: An interrupt is generated after each pulse group is sent.

c) FLD_PWM0_IR_FIFO_IRQ: Enter interrupt when the cfg data inside the FIFO is less than (not including equal to) the set value (trigger_level).

d) FLD_PWM0_IR_DMA_FIFO_IRQ: When the FIFO has finished executing the cfg data sent by DMA, it enters the interrupt.

Interrupts supported by PWM1:

a) FLD_PWM1_FRAME_DONE_IRQ: Each signal frame is completed and an interrupt is generated.

Interrupts supported by PWM2:

a) FLD_PWM2_FRAME_DONE_IRQ: Each signal frame is completed and an interrupt is generated.

Interrupts supported by PWM3:

a) FLD_PWM3_FRAME_DONE_IRQ: Each signal frame is completed and an interrupt is generated.

Interrupts supported by PWM4:

a) FLD_PWM4_FRAME_DONE_IRQ: Each signal frame is completed and an interrupt is generated.

Interrupts supported by PWM5:

a) FLD_PWM5_FRAME_DONE_IRQ: Each signal frame is completed and an interrupt is generated.

A pulse group contains several frames and can be configured via the pwm_set_pwm0_pulse_num function interface:

static inline void pwm_set_pwm0_pulse_num(unsigned short pulse_num).

The value of the IR FIFO mode trigger_level can be configured via the pwm_set_pwm0_ir_fifo_irq_trig_level function interface:

static inline void pwm_set_pwm0_ir_fifo_irq_trig_level(unsigned char trig_level).

Note:

- When responding to an interrupt, there is a time delay of about 2~4 us.

Continuous mode

Function description

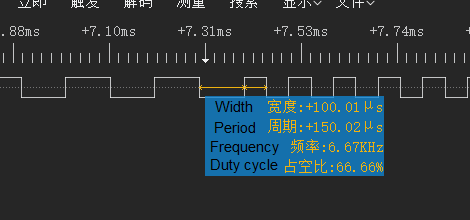

The demo implements the following functions: LED1 will continuously send signal frame (high level time of 50us, period of 100us), at the same time, every time an interrupt is generated, LED4 will be toggled once (the GPIO is a marker signal set to do interrupt test).

Example results

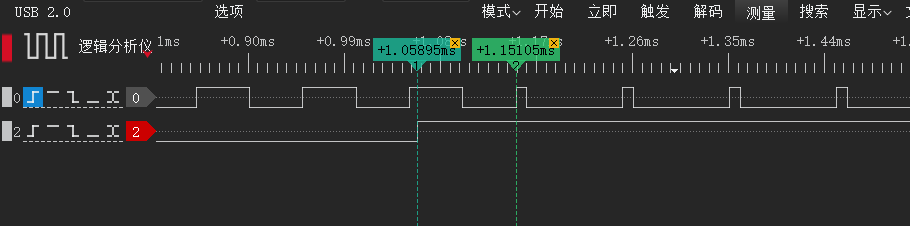

The above figure shows the test results captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED4): is an interrupt marker GPIO, generating an interrupt for each signal frame sent.

The red box indicates: the time delay to generate the interrupt, the CPU needs a certain amount of software and hardware processing time to enter the interrupt.

Other validation results

(1) Stop

Use the following test to verify that in continuous mode, signal will stop immediately after executing stop.

The code implementation is as follows, after the stop, toggle the state of LED3.

pwm_start(PWM_ID);

delay_ms(1);

pwm_stop(PWM_ID);

gpio_toggle(LED3);

Test results are captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is the stop marker GPIO.

As can be seen from the figure, the PWM signal stops immediately after LED3 is toggled.

(2) Duty cycle

Use the following test to verify that in continuous mode, the duty cycle can be updated during the data sending period, and the update of the duty cycle will take effect in the next frame. The code implementation is as follows, after modifying the duty cycle state, the state of LED3 is toggled.

pwm_start(PWM_ID);

delay_ms(1);

pwm_set_tcmp(PWM_ID,10 * CLOCK_PWM_CLOCK_1US);

gpio_toggle(LED3);

Test results are captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is the duty cycle update marker GPIO.

As can be seen from the figure, after LED3 is toggled, PWM modifies the duty cycle to take effect at the next frame.

Counting mode

Choose which interrupt method by using the macro in app_pwm_count.c

#define COUNT_FRAME_INIT 1

#define COUNT_PNUM_INIT 2

#define SET_COUNT_INIT_MODE COUNT_FRAME_INIT

COUNT_FRAME_INIT

Function description:

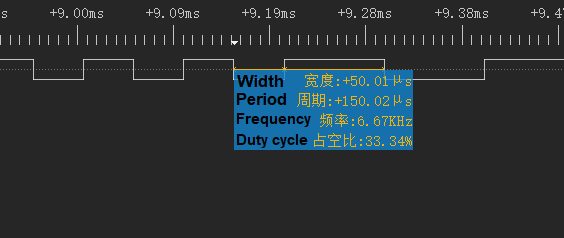

The demo implements the following functions, LED1 will output a number of 16 signal frame (high level time of 50us, period of 100us), at the same time, it generates an interrupt every signal frame sent, , LED4 will be toggled once (the GPIO is a marker signal set to do interrupt test).

Example results:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED4): is an interrupt marker GPIO, generating an interrupt for each signal frame sent.

The red box indicates: the time delay to generate the interrupt, the CPU needs a certain amount of software and hardware processing time to enter the interrupt.

COUNT_PNUM_INIT

Function description:

The demo implements the following functions: LED1 will output a signal frame with a number of 16 (50us high level time, 100us period), and after sending the specified number of pulses, an interrupt will be generated and LED4 will be toggled (the GPIO is a marker signal set for interrupt testing).

Example results:

The details of the red boxes are as follows:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED4): is the interrupt marker GPIO, specify the number of pulses sent out, generate an interrupt.

Red box description: 3us more than 50us, indicating that there is a certain time delay to enter the interrupt and the CPU needs a certain amount of software and hardware processing time to enter the interrupt.

Other validation results

(1) Stop

Use the following test to verify that in counting mode, signal will stop immediately after executing stop.

The code implementation is as follows, after the stop, toggle the state of LED3.

pwm_start(PWM_ID);

delay_ms(1);

pwm_stop(PWM_ID);

gpio_toggle(LED3);

Test results are captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is the stop marker GPIO.

As can be seen from the figure, the PWM signal stops immediately after LED3 is toggled.

(2) Duty cycle

Use the following test to verify that in counting mode, the duty cycle cannot be changed when changing the duty cycle during data sending.

The code is implemented as follows, toggle the state of LED3 after modifying the duty cycle state.

pwm_start(PWM_ID);

delay_ms(1);

pwm_set_tcmp(PWM_ID,10 * CLOCK_PWM_CLOCK_1US);

gpio_toggle(LED3);

Test results are captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is the duty cycle update marker GPIO.

As can be seen from the figure, the signal of PWM does not change after LED3 is toggled.

The test results are as follows:

IR mode

Function description

The demo implements the following functions, LED1 will output 6 pulse groups (each pulse group, the number of pulses is 4, the high level time is 50us, the period is 100us), at the same time, after sending a pulse group, an interrupt is generated, LED4 will be toggled once (the GPIO is a marker signal set to do interrupt test).

Example results

The above figure shows the test results captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is an interrupt marker GPIO, toggle once after a pulse group sent.

The red box indicates: the time delay to generate the interrupt, the CPU needs a certain amount of software and hardware processing time to enter the interrupt.

Other validation results

(1) Stop

Use the following test to verify that in counting mode, signal will stop immediately after executing stop.

The code implementation is as follows, after the stop, toggle the state of LED3.

pwm_start(PWM_ID);

delay_ms(1);

pwm_stop(PWM_ID);

gpio_toggle(LED3);

Test results captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is the stop marker GPIO.

As can be seen from the figure, the PWM signal stops immediately after LED3 is toggled.

(2) Duty cycle

Use the following test to verify that in counting mode, the duty cycle can be changed in the middle, but it will take effect after the current pulse group is executed.

The code implementation is as follows:

pwm_start(PWM_ID);

delay_ms(1);

pwm_set_tcmp(PWM_ID,10 * CLOCK_PWM_CLOCK_1US);

gpio_toggle(LED3);

Test results are captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is the duty cycle update marker GPIO.

As you can see from the figure, the signal of pwm does not change immediately after LED3 is toggled, but takes effect after the current pulse group is executed.

IR FIFO Mode

Function description

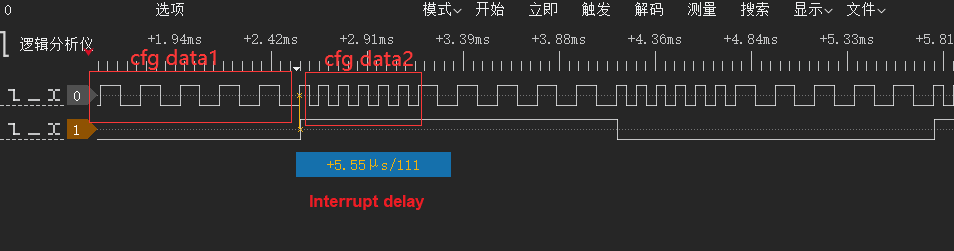

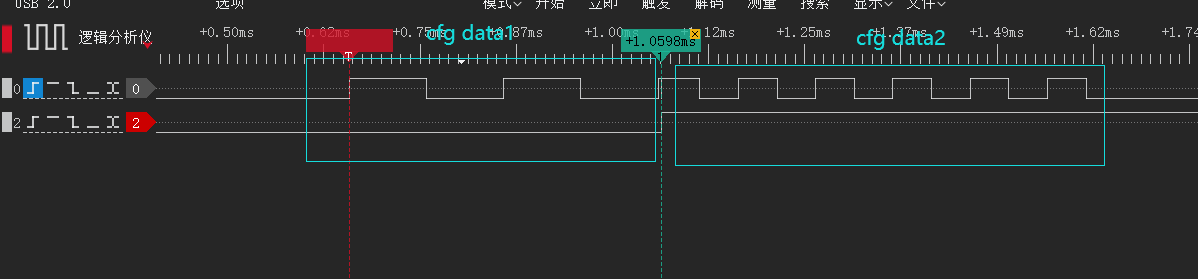

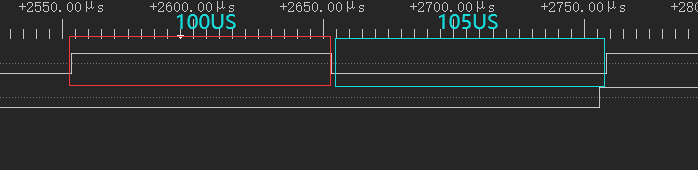

The general flow of the IR FIFO MODE demo is introduced: at the beginning, write two groups of cfg data1, cfg data2 to the FIFO, when the cfg data inside the FIFO is less than (not including equal to) the set value (trigger_level is 1) to enter the interrupt, in the interrupt the same two groups of cfg data1, cfg data2 are configured.

The demo implements the following functions, LED1 is sent in two groups of pulses in sequence and continuously, and the two groups of pulses are set as follows:

(1) cfg data1, high level time of 50us, period of 100us

(2) cfg data2, high level time of 100us, period of 200us

LED4 will be toggled once for each interrupt generated (this GPIO is a marker signal set to do interrupt testing).

Example results

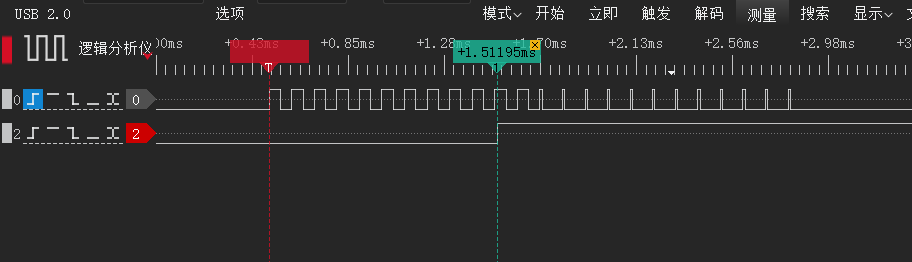

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED4): is the interrupt marker GPIO, when the cfg data inside the FIFO is less than (not including equal to) the set value (trigger_level is 1), toggle once (after the execution of cfg data1, cfg data2 is taken out from the FIFO, the value of cnt is 0, which is less than the trigger level (value is 1), it enters an interrupt).

The red box indicates: the time delay to generate the interrupt, the CPU needs a certain amount of software and hardware processing time to enter the interrupt.

Other validation results

(1) Stop

Use the following test to verify that in IR FIFO mode, after executing stop, it only stops the execution of the current cfg data and does not affect the execution of the cfg data after the fifo.

The code implementation is as follows, after the stop, toggle the state of LED3.

delay_ms(10);

pwm_stop(PWM_ID);

gpio_toggle(LED3);

Test results are captured using a logic analyzer:

Channel 0 (LED1): is the PWM output signal.

Channel 1 (LED3): is the stop marker GPIO.

In the IR FIFO MODE function description:

cfg data1: Number of pulses is 5, high level time is 50us, period is 100us.

cfg data2: number of pulses is 6, high level time is 100us, period is 200us.

As can be seen from the figure, after executing stop, LED3 is toggled, stopping the execution of the current cfg data1 does not affect the execution of cfg data2 behind the fifo.

DMA FIFO mode

Select the working method by using the macro in app_pwm_ir_dma.c

#define PWM_IR_FIFO_DMA 1

#define PWM_CHAIN_DMA 2

#define SET_PWM_DMA_MODE PWM_IR_FIFO_DMA

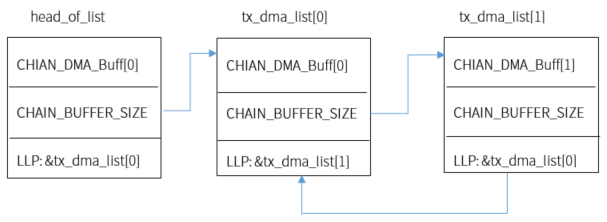

PWM_IR_FIFO_DMA

In IR DAM FIFO Mode, interrupts need to be constantly triggered to request DMA to send cfg data to the FIFO.